尊敬的 TI 团队:

我 目前正在我自己的设计中评估 DRV8316RRGFR 电机驱动器。 我遇到了一个需要您支持的行为:

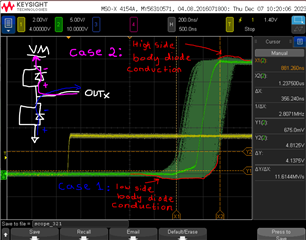

OUTx 引脚的上升沿和下降沿都对控制 PWM 信号 INHx / INLx 具有随机延迟。 尽管已激活延迟补偿、但仍存在此行为。

PWM 边沿的这种非确定性抖动或失准 会导致 随机电流峰值、从而无法进行精确、快速的电流调节。

我已经找到了应用手册 "集成 MOSFET 驱动器中的延迟和死区时间"(https://www.ti.com/lit/an/slvaf84/slvaf84.pdf?ts = 1701773914460)并应用了1.2 µs 的推荐 DLY_COMP。 这对随机抖动没有帮助。

技术细节:

VM = 24V

PWM 频率= 40kHz

SPI 配置:

µs 率:200V/μ s

CSA 增益0.6V/A

DLY_COMP_EN:已启用

DLY_TARGET:1.2 µs (µs 数据表中关于压摆率200V/μ s 的建议)

PWM_100_DUTY_SEL:40kHz

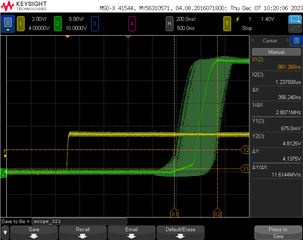

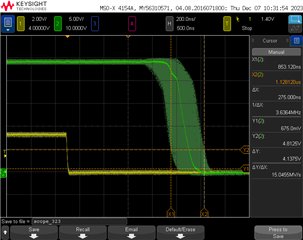

我将添加两个示波器录制文件:

黄色:来自微控制器的 PWM 控制信号 INHC、被触发。

绿色:PWM 输出信号输出。

激活持久性后、可以看到抖动+/- 137nS。 偏差量因 OUTx 信号和 OUTx 信号而异。

这种行为是由配置还是外部接线造成的? 或者这是 DRV8316的特性吗? 增加延迟补偿时间是否有帮助?

此致、

涅狄格特