大家好、

DRV8714 SPI 时钟应为16位。 当我们在一个 nSCS 中发送32位时钟时、这会触发 SPI 时钟故障吗?

在测试过程中、我们没有收到 SPI 时钟故障指示。

我可以知道"无效 SPI 锁定帧"的定义是什么吗?

谢谢!

此致!

弗兰克

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

DRV8714 SPI 时钟应为16位。 当我们在一个 nSCS 中发送32位时钟时、这会触发 SPI 时钟故障吗?

在测试过程中、我们没有收到 SPI 时钟故障指示。

我可以知道"无效 SPI 锁定帧"的定义是什么吗?

谢谢!

此致!

弗兰克

您好、Ryan,ñ a

我们已读取寄存器、而不会监控 nFAULT。 在这种情况下、寄存器 IC_STAT1的 SPI_OK 位始终为1。

2.可以从设备中正确写入和读取数据。

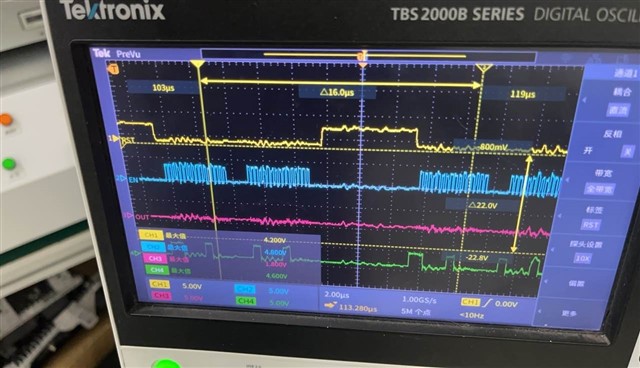

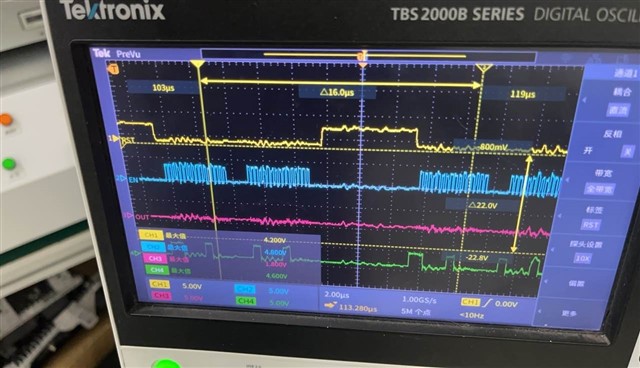

在图片中、您可以看到两个16位时钟之间的时间约为1.2us。 我们想知道 未设置 SCLK_FLT 与它相关(1.2us)。

我们想知道导致 SCLK_FLT 的所有条件。 至少目前、 我们在一个 nSCSwe 中发送了32位时钟、但尚未触发 SCLK_FLT。

嘿、荣来、

请您多给我们有关该器件的专家一天时间、以了解详情。

我们是否可以假设 FIRT 16位数据已接收并正确响应,而第二个16位数据已被忽略?

根据数据表、SDI 引脚接收大于或小于16位的数据会导致一个 SCLK_FLT、并忽略整个事务。 您已确认事务后 SCLK_FLT 未触发、且事务已成功写入器件? 只是想确保我们正确理解问题。

您是否能够在包含16个时钟脉冲的两个灯串之间使用更短的时间来测试它?

此致!

雅各布

您能在16个时钟脉冲的两个字符串之间用更少的时间来测试它吗? [/报价]您可以看到、当 在包含16个时钟脉冲的两个字符串之间使用更少的时间读取同一寄存器(IC_STAT1)时、响应数据会有所不同。

嘿、荣来、

Hmm 很有趣。 我已经将此帖子发布给了我们的设计团队、并会让您知道他们说的是什么、尽管这可能是合理的警告、但也可能需要几天时间。

我们是否可以假设 FIRT 16位数据已接收并正确响应,而第二个16位数据已被忽略?

如果这是您的测试显示的内容、我可以对这个问题说"是"。 首先对其进行1次测试。 读取所有寄存器2。 写入寄存器。 3.读取所有寄存器并确认仅更改了您写入的寄存器。 在几个寄存器上进行测试、如果结果得到证实、除非我能得到更明确的答案、否则我现在继续提出这个结论。

此致!

雅各布

嘿、荣来、

我收到了设计的反馈:

在 RTL 中、看起来前16位被忽略、后16位被接收。 具有32位时钟脉冲的 SPI 帧不安全、它可能会损坏寄存器数据、如最后16位中所述。

需要在 RTL 仿真中检查以在 SPI 接口 IP 中再次确认此问题。 我们目前还没有准备好仿真。 这需要一些时间。

我们可以通过以下方式在 EVM/测试板中进行确认: 读取从第3个字节指向的寄存器地址中发送的第4个字节的数据。

您能让客户尝试测试这个粗体部分吗? 我目前没有带宽来深入研究此 EVM 以创建适用于32位 SPI 的定制固件、但客户似乎已经拥有此带宽。

谢谢。

雅各布