工具与软件:

你(们)好。

对可应用于 Vinx 的波形有哪些要求?

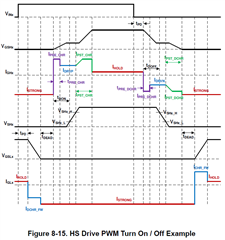

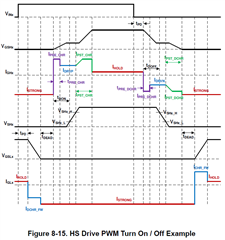

正如我从下图中可以看到的、我认为如果 Vinx 在以下总时间内没有输出高电平、那么上行或下行 FET 将半接通。

"tpd"+"VGSLx"+"tDEAD"+"tDON"+" VSHx 从 VSHx_L 到 VSHx_H"+"tPST_CHR"的上升时间

您是否同意上述观点?

此外、在这种情况下、"TPD"时间定义在哪里?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

你(们)好。

对可应用于 Vinx 的波形有哪些要求?

正如我从下图中可以看到的、我认为如果 Vinx 在以下总时间内没有输出高电平、那么上行或下行 FET 将半接通。

"tpd"+"VGSLx"+"tDEAD"+"tDON"+" VSHx 从 VSHx_L 到 VSHx_H"+"tPST_CHR"的上升时间

您是否同意上述观点?

此外、在这种情况下、"TPD"时间定义在哪里?

您好!

感谢您的问题

>>如果对 Vinx 应用非常低的占空比,我认为输出将在 Vgshx 达到 Hi 之前关闭。

是的、这是正确的。

>>我想计算使 Vgshx 达到高电平所需的占空比

这取决于客户的应用、例如外部 FET、DRV 的 IDRIVE 寄存器设置等。 输出的上升和下降时间不受 DRV 性能的影响。

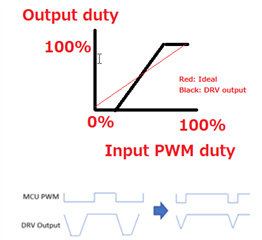

基于以上背景、下面是一个示例。

I customer 的输出上升和下降时间为5us、PWM 频率为20kHz (50us)、5usec 为20kHz 的10%。

客户在 MCU 的 PWM 为0-10%和90-100%时没有良好的输出脉冲。

此致

森田真也