工具与软件:

您好!

我使用 SPI 评估 DRV8452。

正常操作没有问题。

当我停止步进脉冲时,"激发模式返回?" 电荷积聚现象。

由于此问题、无法返回到目标位置。

我是否配置不正确?

请告诉我。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Yamasuge-San:

感谢您的澄清。 我现在看到了。 您正在查看 AOUT1/2和 BOUT1/2引脚相对于 GND 的电压输出波形。 这些是 TON 周期。 应该观察通过线圈 A 和 B 的电流波形。当步进脉冲停止时、根据分度器表、索引将在最后一个位置停止、并且输出线圈电流取决于所使用的步进模式、请参阅数据表中的表7.7至7.9。

停止时、如果 A 或 B 线圈中的电流不为零、则您将在 A 或 B 或两个输出中看到相应的激励模式(该电流电平的电流调节)。 即使电流为零、输出端也可能有一些 TON 和 tOFF 周期。 这是正常行为。

此致、Murugavel

尊敬的 Yamasuge-San:

我尝试复制您提到的行为。 但我无法再现它。 请参阅下面的捕获。 我预计电机电流不会从分度器的步进停止位置变化、除非以最低延迟时间启用转矩 DAC 设置或静止省电功能。 分度器在下一个 STEP 脉冲之前不应移动。 STEP 脉冲输入引脚必须始终保持逻辑低电平、直到施加脉冲、然后返回到零。

我还怀疑您运行的可能是空载步进电机。 在这种情况下、电机惯性可能会导致物理过冲、该过冲也可能在电流波形中显示为伪影。 解决方法是为电机加载以实现适当的阻尼。 我希望这对您有所帮助。 谢谢你。

此致、Murugavel

尊敬的 Yamasuge-San:

根据我们的内部逻辑设计 、我们建议在空闲时使 STEP 输入逻辑为低电平。 阶跃输入的每个上升沿、分度器前进一步。 当 DRV8452 SPI 版本中的 STEP 边沿位被设置时、STEP 输入会使上升沿和下降沿的分度器提前。

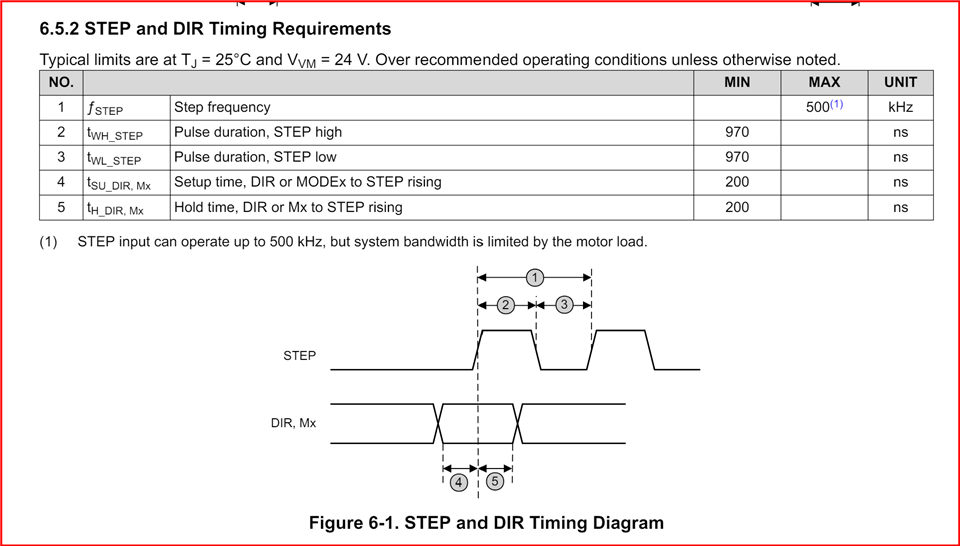

下面是数据表中 STEP 输入- STEP 边沿未启用的时序图。 空闲高电平可能会导致分度器不正确地运行步进控制。

此致、Murugavel