工具与软件:

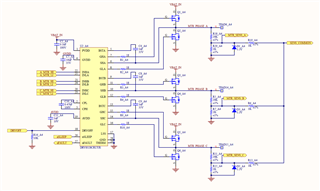

我将使用 DRV8328提出一个新设计、该设计的某些设置会导致 MOSFET 烧毁。

我认为这是由于开关时间太短、因此我将栅极电阻器增加到100欧姆、而不是原理图中的18欧姆。 VDS 下降时间从40ns 增加到180ns。 我的死区时间大约为2000ns。

即使在断开栅极电阻器并增加死区时间后、MOSFET 仍在燃烧。 开始。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

我们使用的是 SQS174ELNW-T1_GE3。 在25V PVDD/VBAT_IN 上运行。

https://www.mouser.com/ProductDetail/78-SQS174ELNW-T1_GE3

当前未监视 nFAULT 引脚。

您好、Alex、

我需要确认、但我怀疑 GHx 和 GLx 节点上的振铃可能会导致击穿事件。 您可以测量高于接地(对于 GLx)或相电压(对于 GHx)的振铃高度、并将其与 MOSFET 的阈值电压进行比较以确认。

一种选择是进一步增加栅极电阻以降低压摆率、或者您可以选择具有更高 Qgd 的 MOSFET。 或者、您也可以参阅此应用手册以了解有关创建缓冲器电路以减少振铃的信息: https://www.ti.com/lit/an/slvaf66/slvaf66.pdf?ts = 1722634648974。 最后、请确保电路板布局布线遵循本应用手册( https://www.ti.com/lit/an/slva959b/slva959b.pdf)中概述的最佳实践。 栅极驱动器和栅极之间的长布线会引入寄生电感、从而增加振铃。

最后、您使用的 PWM 频率是多少? 高开关频率 通常还会增加功率损耗、从而使 MOSFET 升温。

此致!

Davis

谢谢 Davis。

PWM 频率为24kHz 至48kHz。 栅极布线很短、大约为7mm。

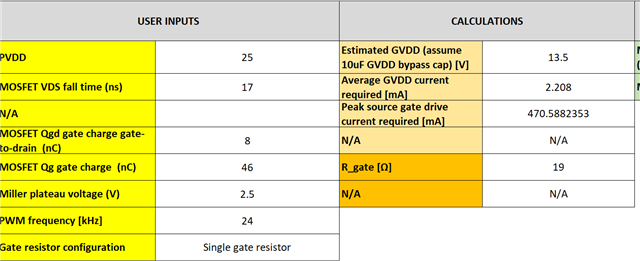

SQS174ELNW 栅极电阻计算器。 它们具有较低的 Qg 和 Vth。

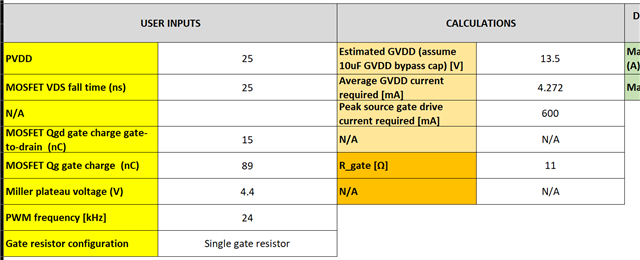

我希望切换到 IAUCN08S7N013、它具有更高的 Qg 和更低的 RDS。

GATE 电阻计算器显示了一个用于这些器件的11 Ω 电阻、数据表下降时间为25ns。

我遇到的一个问题是关于 VDS 下降时间。 这应该是 FET 数据表中的下降时间、还是所需的下降时间?

您好、Alex、

我认为 FET 数据表中的下降时间是一个取决于设计的动态参数、因此需要计算器中的下降时间、从而成为设计的产物。 计算器将给出在理论上应实现所需下降时间的栅极电阻。 由于电流更高、VDS 下降速度会更快、可以为固有栅漏极电容提供更多电荷、因此压摆率与栅极电阻成反比。

我还建议确保您的布线尽可能宽。 如果正在发生跨导、电路板设计技术加上更高的栅极电阻和 Vth 应该有望停止跨导。

此致!

Davis

您好、Alex、

很抱歉有其他回复。 与我的团队讨论后、我只想确认提高压摆率和阈值电压应该会有所帮助。 有关节点振铃解决方案的更多信息、请参阅此常见问题解答(#8): https://e2e.ti.com/support/motor-drivers-group/motor-drivers/f/motor-drivers-forum/1176539/faq-quick-guide-to-debugging-common-issues-in-bldc-motor-drivers。

与24kHz 相比、48kHz 的 PWM 频率将 产生更多的开关损耗、并且较长的死区时间会通过低侧 MOSFET 中的体二极管导通产生更多损耗。 这些损耗源会导致 MOSFET 中的热损耗、但它们不会被视为过流事件。

如果有帮助、请告诉我。

此致!

Davis