工具与软件:

DRV8353驱动波形测试:

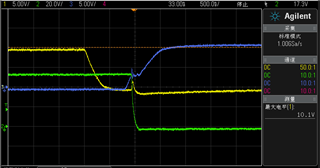

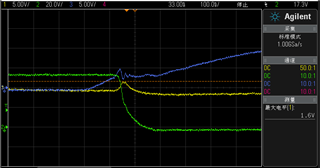

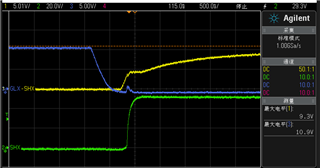

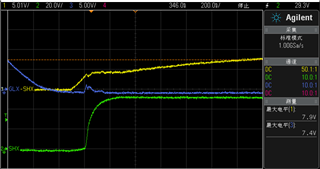

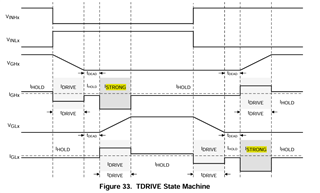

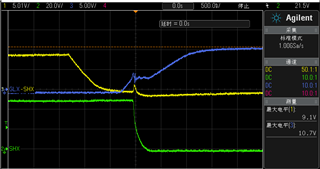

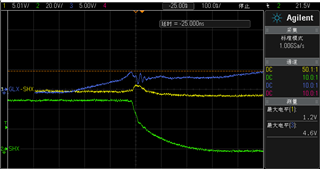

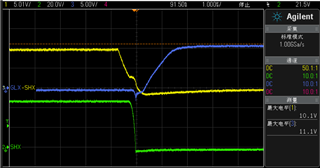

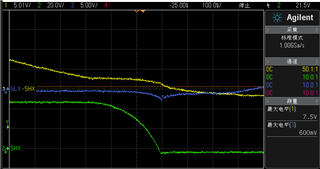

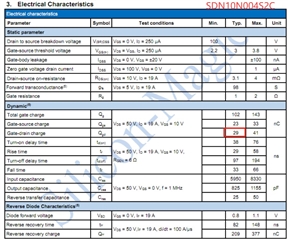

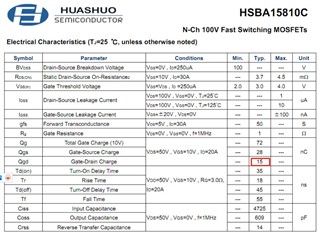

48V、PWM 20kHz、双路 MOSFET、灌电流600mA、拉电流400mA 、死区时间200ns

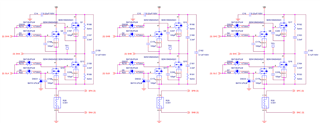

原理图如下:

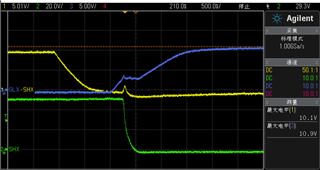

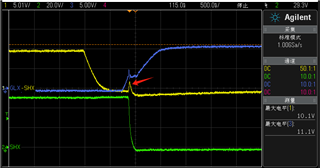

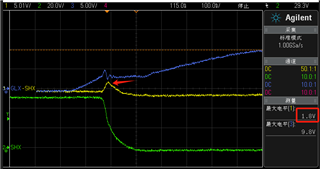

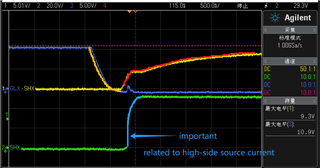

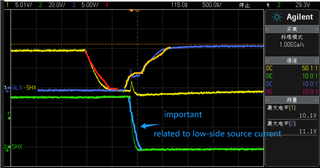

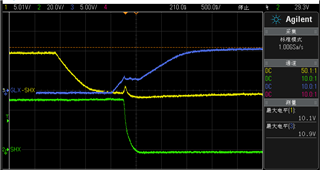

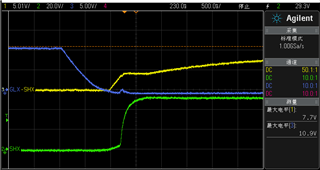

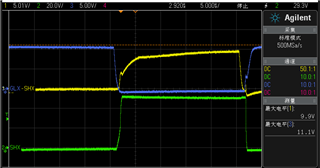

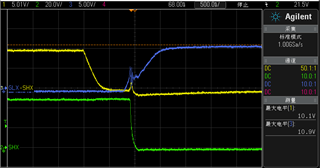

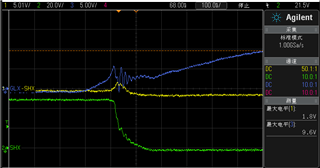

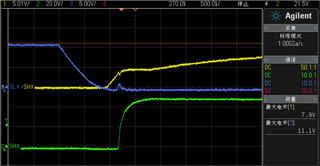

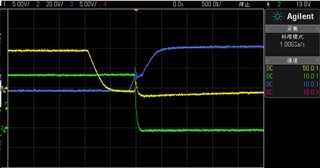

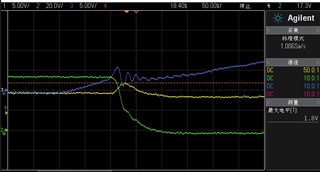

1通道(黄色) GHC-SHC、上桥 VGS 电压

2通道(绿色) SHC、相电压

3通道(蓝色) GLC、下桥 VGS 电压

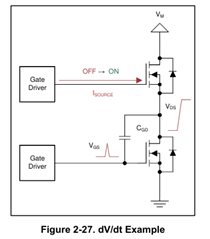

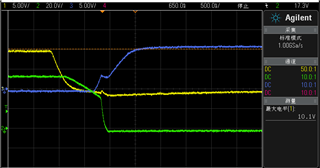

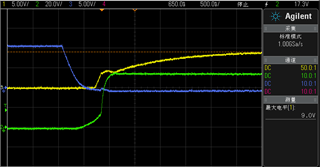

下桥 VGS 具有明显振荡、上桥也会出现电压上升。 它是否合理或者是否有隐藏的危险。 我尝试抑制振荡的振幅:

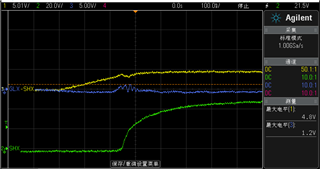

VGS 之间并联了1)100K 电阻器、没有明显变化

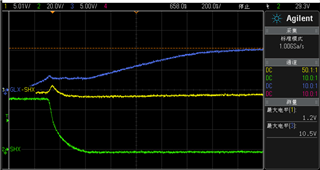

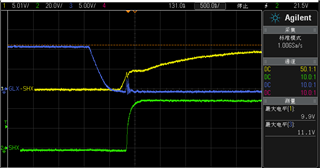

2)降低驱动电流,灌入300mA 拉电流300mA ,下降沿减慢,但振动仍然存在,振幅应更低

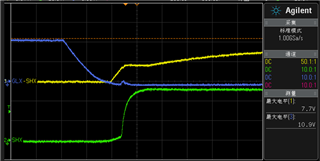

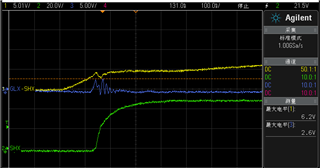

3)增大驱动电流,灌入800mA 拉电流550ma ,边沿抖动更多,但振动仍在增加

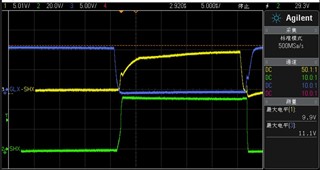

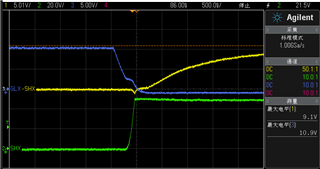

)μ A 驱动电流保持不变(灌电流600mA 拉电流400mA)、并且在 GS 和100K 下拉电阻之间没有100pF 电容时、振荡略有增加

)驱动电流(灌电流600mA 拉电流300mA)并添加100pF。 如果没有100K 下拉电阻、振荡会略有增加、这可以吗?