工具与软件:

电机驱动器团队工作、

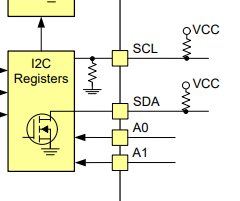

DRV8214上 SCL 的内部下拉 电阻会导致一个客户的低功耗项目消耗大约10uA 的电流。 是否有办法在空闲时禁用此下拉电阻、或以其他方式避免这种电流消耗?

在数据表第12页中:

谢谢!

Darren

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Darren、您好!

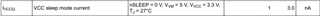

数据表中有两种睡眠电流规格:IVMQ 和 IVCCQ。 内部逻辑由 VCC 供电、因此当器件处于睡眠模式时、IVCCQ 将是在该状态下向内部逻辑提供的数字逻辑电源。 通常在没有输入或外部负载(包括上拉电阻)的情况下给出满足此规格的测试条件。

在此状态下、外部上拉电阻会导致该引脚消耗任何漏电流。

对于他们可以从 SCL 引脚汲取的电流大小是否存在设计限制或者他们是只是在尝试最大化功耗吗?

此致!

David