工具与软件:

您好、先生

问题:

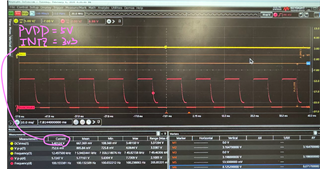

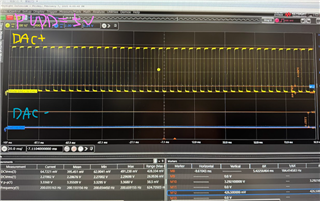

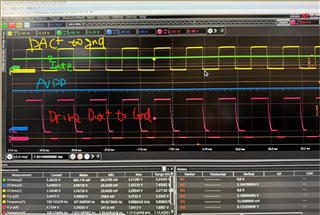

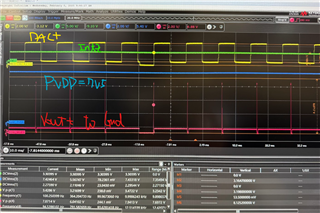

1.我们使用 PVDD 5V 向 DRV2511输入正电压 PWM 信号(0~3V3)=>驱动器可以将正常输出幅度从3V3调到5V

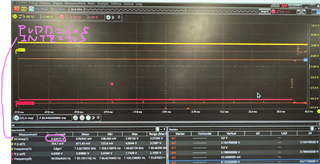

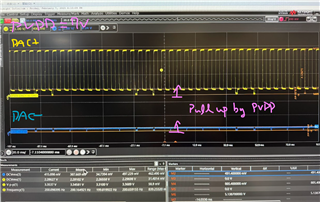

2.由于 PVDD 6~18V =>驱动器将产生植入式波形而不是正常的 PWM 波形。

=>我们确认 PVDD 的电源充足。

=>您可以帮助解决这个问题吗?

条件:

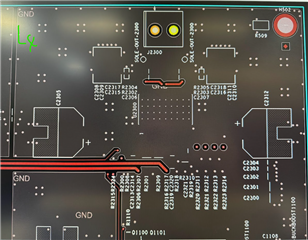

1.驱动器输出:空载

2.我们的原理图可显示为附文。(遵循 DRV2511 EVM 和器件)

3.设置

- FS1、FS2 =低电平

-待机=低

-增益= 20k Ω 至接地

- Reg = 1uF 至接地