工具/软件:

我会尽量详细地解释这个问题。

系统:

电容式触控传感器连接到 MSP430F5505 MCU。 用户将手指放在传感器上、传感器会进行一些处理(其中包含 ASIC)。 当传感器准备好发送数据时、它会将 RDY 信号拉至低电平。 RDY 信号作为输入馈送到 MCU。

时钟配置:

4MHz 有一个外部晶体用于为 MCU 提供时钟。 MCU 中有三个主时钟-主时钟、子主时钟和备用时钟。 I2C 外设从其 SCL 的子主时钟获取时钟。

XT2 (4MHz)-> FLL (这里我们进行乘法并发送 MCLK=SMCLK = 24MHz)-> DCO -> MCLK 和 SMCLK

问题:

在主循环中、只要我们进入、我就有一个如下所示的测试代码:

```μ s

静态易失性 uint32_t GETmclk = 0;

静态易失性 uint32_t GETsmclk = 0;

静态易失性 uint32_t GETaclk = 0;

while (1)

{

__ no_operation ();

__ no_operation ();

GETsmclk = UCS_getSMCLK ();

GETmclk = UCS_getMCLK ();

GETaclk = UCS_getACLK ();

__ no_operation ();

}

```μ s

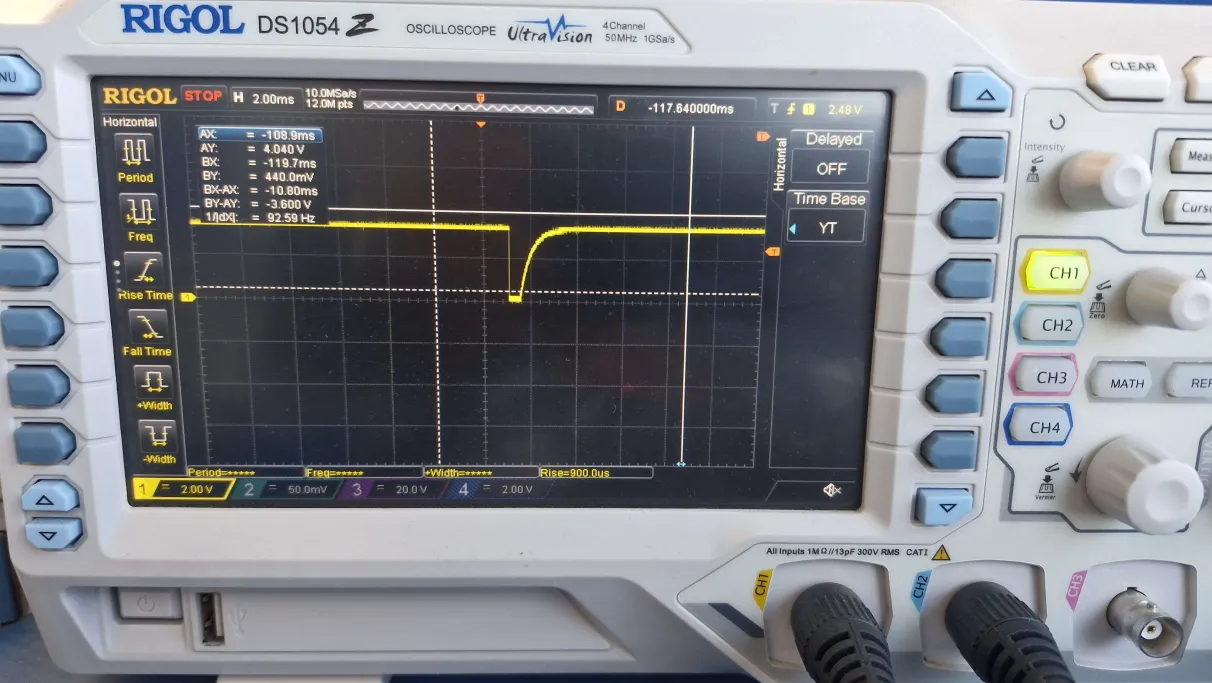

当我注释在 while 循环中编写的代码时、RDY 引脚的行为就像悬空一样。 仅当用户触摸传感器时、引脚才应变为低电平、但在未注释代码的情况下、即使用户未触摸传感器、引脚也会变为低电平。

所以我想:"嘿,让我把 RDY(输入引脚)拉高",它有效。 使用软件启用上拉引脚后即可正常工作。 但还有另一个问题:

当我使用 REFOCLOCK 运行 SMCLK、并且 SMCLK 以低得多的速度运行时、即使 GPIO 引脚未被拉高、也不会出现问题。

所以我想:当 SMCLK 来自 DCO 时、我来尝试减少 SMCLK。 这没有解决问题。 我想知道发生了什么。

为什么在主循环中读取 SMCLK 和 MCLK 对 PIN 悬空有帮助? 它是否以某种方式与时钟同步? 为什么从 REFOCLOCK 为 SMLCK 提供源会有所帮助?

clock init 如下所示:

```μ s

静态 void initClock (void)

{

GPIO_setAsPeripheralModuleFunctionInputPin (GPIO_PORT_P5、GPIO_P2 | GPIO_PIN3);

UCS_setExternalClockSource (0、XT2_FREQ);

UCS_TURNOnXT2 (UCS_XT2_DRIVE_4MHz_8MHZ);

while (UCSCTL7和(XT2OFFG | DCOFFG))

{

UCSCTL7 &=~(XT2OFFG | DCOFFG);

SFRIFG1 &=~OFIFG;

}

UCS_initClockSignal (UCS_FLLREF、UCS_XT2CLK_SELECT、UCS_CLOCK_DIVIDER_4);

UCS_initFLLSettle (MCLK_kHz、MCLK_FLLREF_RATIO);

UCS_initClockSignal (UCS_SMCLK、UCS_DCOCLK_SELECT、UCS_Clock_divider_1);

//由于我们不使用 ACLK、因此我们可以将其禁用。

UCS_disableClockRequest (UCS_ACLK);

//配置 USB PLL

USBKEYPID = 0x9628;//解锁 USB 配置寄存器

USBPLLDIVB = 0;//将 XT2除以1 (XT2 = USB PLL 的4 MHz 输入)

USBPLLCTL = UPLLEN | UPFDEN;//启用 USB PLL 和频率检测器

//等待 USB PLL 锁定

while (USBPLLIR 和 USBOORIFG);

USBKEYPID = 0x9600;//锁定 USB 配置寄存器

}

#define MHz ((uint32_t) 1000000)

#define XT1_FREQ ((uint32_t) 32768)

#define XT2_FREQ ((uint32_t)(4*MHz))

#define MCLK_FREQ ((uint32_t)(24*MHz))

#define SMCLK_FREQ ((uint32_t) MCLK_FREQ)

#define XT1_kHz (XT1_FREQ / 1000)

#define XT2_kHz (XT2_FREQ / 1000)

#define MCLK_kHz (MCLK_FREQ / 1000)

#define SCALE_FACTOR ((uint8_t) 4)

#define MCLK_FLLREF_RATIO (MCLK_kHz/(XT2_kHz/比例因子)

```μ s

总结如下:

-当 while (1)内的内容被注释掉时(即

GETmclk = UCS_getMCLK ()和相关行)、RDY 行开始

就好像它是浮动的。

-在 RDY 上启用内部上拉可稳定它并防止错误

进行触发。

-对 SMCLK 使用 REFO (而不是 DCO @ 24 MHz )也可以防止 RDY

防止错误地变为低电平、即使没有上拉电阻也是如此。

-降低 SMCLK 频率,同时仍从 DCO 提供它

无法解决问题。

-读取时钟值的行为(如 UCS_getSMCLK ())

主环路以某种方式稳定 RDY 线路行为。