主题中讨论的其他器件:MSPM0G3519、 SysConfig

工具/软件:

TI 团队大家好、

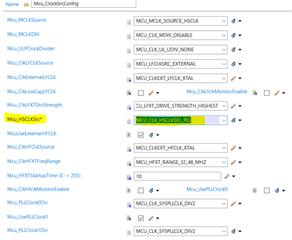

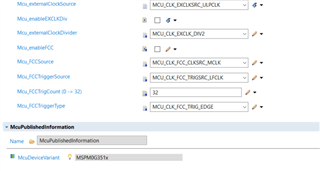

我在 MCU 时钟配置期间遇到了问题。 当 我尝试选择 MCLK 的时钟源 作为 HSCLK 时、我们可以在下图中看到、和 MCU 上的 i 闪存代码时、MCU 不会运行并进入不可预测的状态。 即使我不能 像以前那样刷新它。 我是否需要进行任何特定的设置?

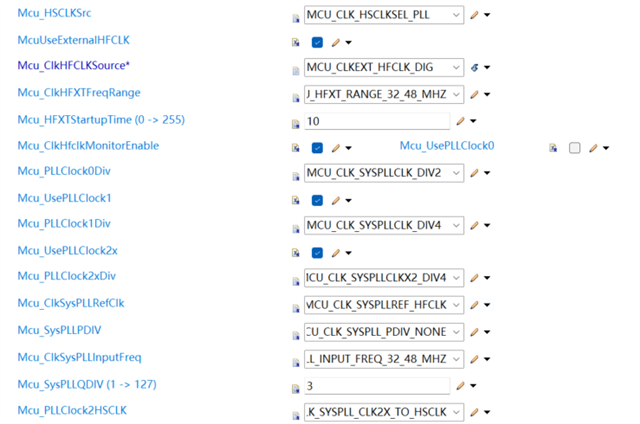

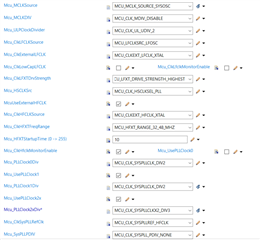

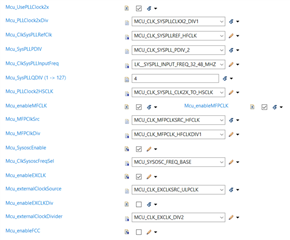

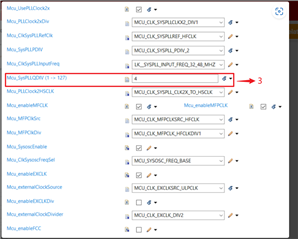

根据技术参考手册、 SYSPLLCLK0 或 SYSPLLCLK2X 作为的来源 HSCLK 然后再设置 HSCLK 作为的时钟源 MCLK。 这是通过 MCU_HSCLKSrc 选择来完成的吗?

。

我正在选择 MCU_HSCLKSrc 如下:

我是否需要检查任何其他参数?

此致、

Rohidas Khurange