工具/软件:

在我的应用程序中、主代码启动后进入 LPM3 模式 。 在以下条件下、应用将退出 LPM3:

-

每个都会发生中断 15.625ms 、并为其 ISR 提供服务 不退出 LPM3 模式 。

-

每一次 125ms 、系统使用指令退出 LPM3、

LPM4_EXIT为提供服务 超级循环 (while(1U)) 一次 、然后返回到 LPM3 模式。 该循环每 125ms 重复一次 。 -

这两者都是如此 LPM3 和活动模式 、 UART 保持有效 并使用运行 SMCLK 配置任何功能 、在上运行 频率与 MCLK 相同 (8MHz ) 。

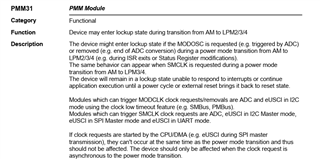

根据上述条件、 此情况是否属于器件勘误表范围 声明:

“器件可能会在从 AM 转换到 LPM2/3/4 期间进入锁定状态。 在从 AM 转换到 LPM3/4 的电源模式期间请求 SMCLK 时找到。“

如果是这样、则如何退出该锁定状态。