主题中讨论的其他器件:UNIFLASH、 MSP-FET、 MSP430FR5994

您好!

我们遇到了 CryptoBSL 进入序列无法持续运行的问题。

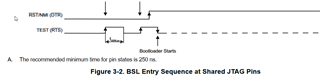

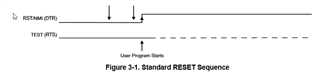

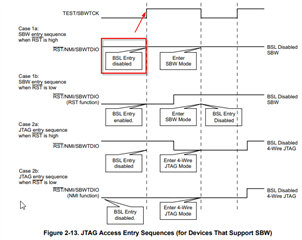

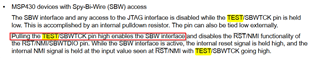

1)标准复位-无法复位 MCU、RST 上持续12us 注意:复位之间的时间相差1 - 5秒 2)标准复位-无法复位 MCU、RST 上持续时间为12us 3) CryptoBSL 进入序列-轮询0x48 50毫秒后失败(ACK 失败) 4)标准复位-成功、RST 上持续时间为12us 5)标准复位- 无法复位 MCU、RST 上12us 持续时间 6)标准复位-无法复位 MCU、RST 上12uS 持续时间 7) CryptoBSL 进入序列-轮询0x48 10ms 后成功 8)标准复位-成功、RST 上12uS 持续时间 9)转至步骤1

1)标准复位-成功、RST 上12us 持续时间 2)标准复位-成功、RST 上12us 持续时间 3) CryptoBSL 进入序列-轮询0x48后10ms 成功 4)标准复位-成功、RST 上12us 持续时间 5)转到步骤1

提前非常感谢您对此提供的帮助!