请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

我的项目必须将 MCLK 格式1M 更改为38400Hz 、然后接收(FLL 参考时钟为 XT1)

我的项目尝试通过使用差分 MCLK 在第1个故障边沿打开/关闭 LED。

1. MCLK = 1MHz、LED 工作。

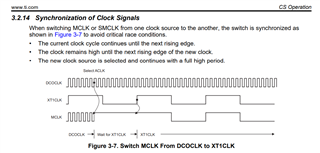

2.将 MCLK 更改为使用 XT1振荡器(38400Hz )针对4位低电平的 LED 延迟。 (请参阅图片中的)

我可以解决这个延迟问题吗?

我的代码:

int main (空)

{

WDTCTL = WDTPW | WDTHOLD; //停止看门狗计时器

clock_setup(); //将 DCO 配置为1MHz,默认为 MCLK 的时钟源

PM5CTL0 &=~LOCKLPM5; //禁用 GPIO 上电默认高阻抗模式

//将 P1.5配置为中断输入

P1DIR &=~(BIT5); //将 P1.5配置为输入方向引脚

P1OUT |= BIT5; //将 P1.5配置为上拉

P1REN |= BIT5; // P1.5上拉寄存器使能

P1IES |= BIT5; // P1.5高-->低边沿

P1IFG &=~(BIT5); // P1.5 IFG 被清除

P1IE |= BIT5; // P1.5中断被启用

P1SEL0 = BIT6 | BIT7; // UCA0 RXD 和 TXD P1.6/P1.7

P1DIR |= BIT0; //将 P1.0/LED 设置为输出方向

P1OUT &=~BIT0; // P1.0 LED 关闭

/*配置 UART

BRCLK = 38400Hz 时* 4800波特

* UCOS16 = 0

* UCBRx = 8

* UCBRFx = 0

* UCBRSx = 0

*

UCA0CTLW0 |= UCSWRST; //将 UART 模块保持在复位模式

UCA0CTLW0 |=(UCPEN|UCPAR); //偶数奇偶校验

UCA0CTLW0 |= UCSSEL_1; //从复位中释放并将 ACLK = 38400设置为 UCBRCLK

UCA0BRW = 8; // 38400/4800 - INT (38400/4800)= 8.

UCA0MCTLW = 0x0000; // eUSCI_A0调制控制字寄存器:38400/4800 - INT (38400/4800)= 0

// UCBRSx 值= 0x00

UCA0CTLW0 &=~UCSWRST; //初始化 eUSCI

UCA0IE |= UCRXIE; //启用 USCI_A0 RX 中断

UCA0IE |= UCSTTIE; //启用 USCI_A0起始位(RX)中断

//针对 LED 开/的一些编码、MCLK = 1MHz

//测试现在正常工作

/*将 MCLK 更改为 xt1 (38400Hz) */

CSCTL4 = SELMS_XT1CLK | SELA_XT1CLK; //设置 ACLK = XT1CLK = 38400Hz

UCA0IE &=~UCTXIE; //禁用 TX 中断

UCA0IE &=~UCRXIE; //禁用 RX 中断

UCA0IE &=~UCSTTIE; //起始位中断不起作用

for (;;){

__no_operation(); //用于调试

}

}

#if defined (__TI_Compiler_version__)|| Defined (__IAR_systems_ICC__)

#pragma vector=Port1_vector

_interrupt void Port_1 (void)

#Elif defined (_GNU_)

void __attribute__((interrupt (Port1_vector))) Port_1 (void)

其他

错误编译器不受支持!

#endif

{

P1OUT ^= BIT0; // P1.0 LED 切换

P1IFG &=~BIT4; //清除 P1.5 IFG

}

void clock_setup(){

P2SEL1 |= BIT6 | BIT7; // P2.6~P2.7:晶振引脚

操作

{

CSCTL7 &=~(XT1OFFG | DCOFFG); //清除 XT1和 DCO 故障标志

SFRIFG1 &=~OFIFG;

} while (SFRIFG1和 OFIFG); //测试振荡器故障标志

BIS_SR_register (SCG0); //禁用 FLL

CSCTL3 |= SELREF_XT1CLK; //将 XT1设置为 FLL 基准源

CSCTL1 = DCOFTRIMEN_1 | DCOFTRIM0 | DCOFTRIM1 | DCORSEL_0; // DCOFTRIM = 3、DCO 范围= 1MHz

CSCTL2 = FLLD_0 + 25; //将 FLL 设置为1MHz

_DELAY_CYCLES (3); //等待稳定的时间

_BIC_SR_register (SCG0); //启用 FLL

Software_Trim (); //软件调整以获得最佳 DCOFTRIM 值

CSCTL4 = SELMS_DCOCLKDIV | SELA_XT1CLK; //设置 ACLK = XT1CLK = 38400Hz

//默认:DCOCLK = MCLK 和 SMCLK 源

//现在 osc 正在运行使能故障中断

SFRIE1 |= OFIE; // DCOCLK = MCLK 和 SMCLK 源

}