Other Parts Discussed in Thread: MSP430F2619

主题中讨论的其他器件:MSP430F2619

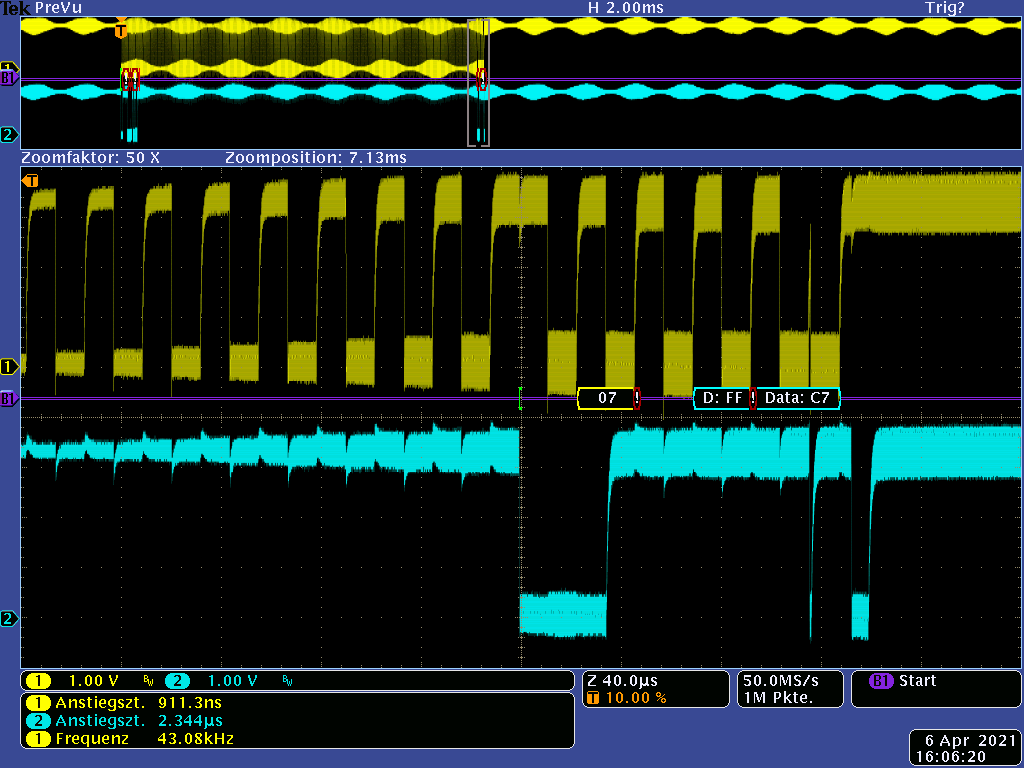

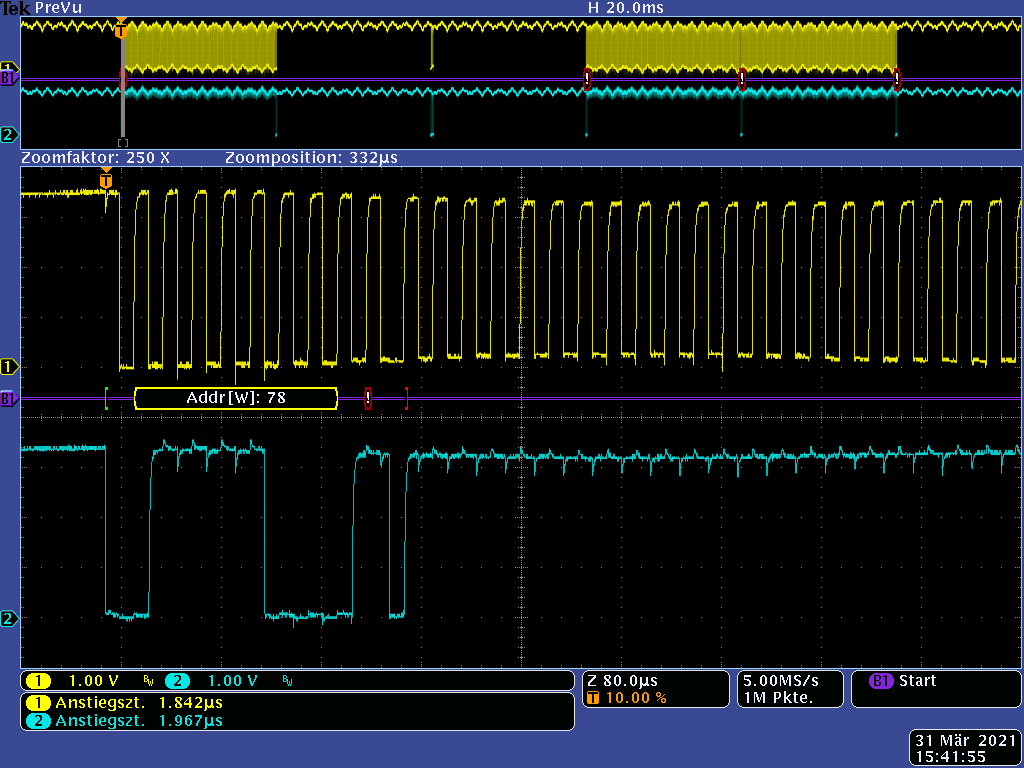

在 EMC 测试期间、我们注意到以下情况:

(参考所附 图像)

- 传输在第一个1位被中止。 我们假设 USCI 此时检测到仲裁丢失错误、因为传入的射频会使信号失真。

- 为什么 USCI 继续生成 CLK 时钟? 我们是否可以采取任何措施来防止这种情况?

- 在第二次传输开始之前、USCI 被软件复位并重新初始化。 时钟一直运行、直到这个软件启动的复位。 为什么它一直运行到这里?

- 根据系列用户指南、如果 USCI 检测到仲裁丢失错误、UCALIFG 将被置位。 当 UCALIFG 被置位时、UCMST 位被清零并且 I2C 控制器成为一个从器件。 但是在 UCMST 被清零后、USCI 不应该生成任何时钟!!! (我们都在单主控模式下运行、从器件不会生成任何时钟!)

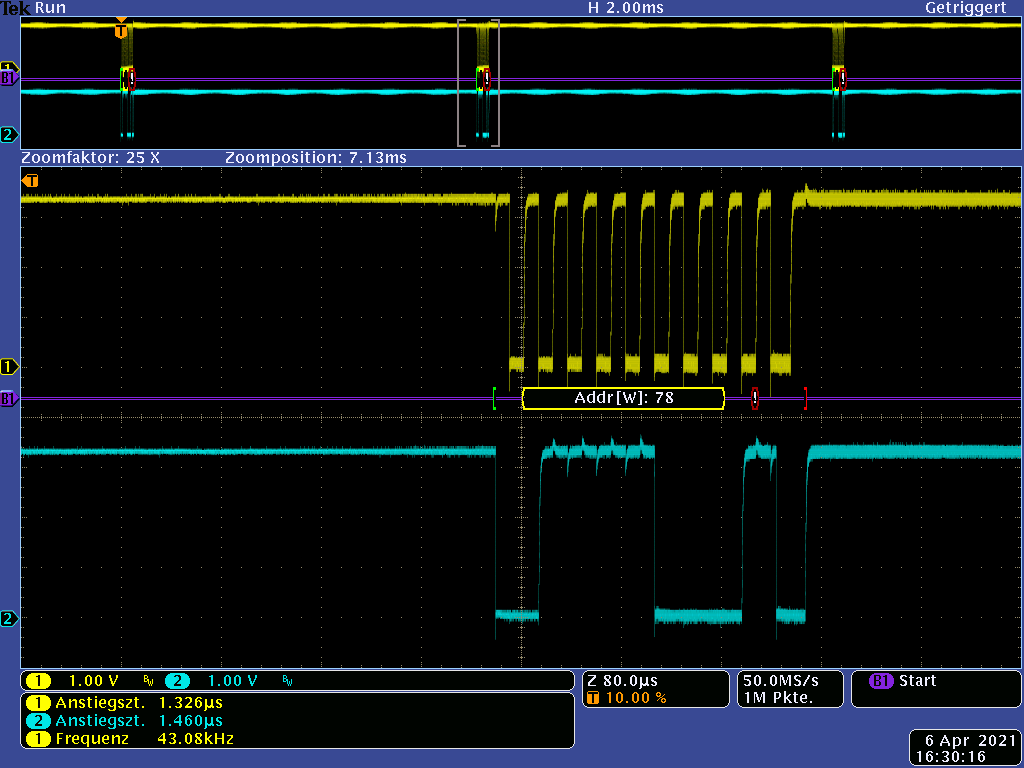

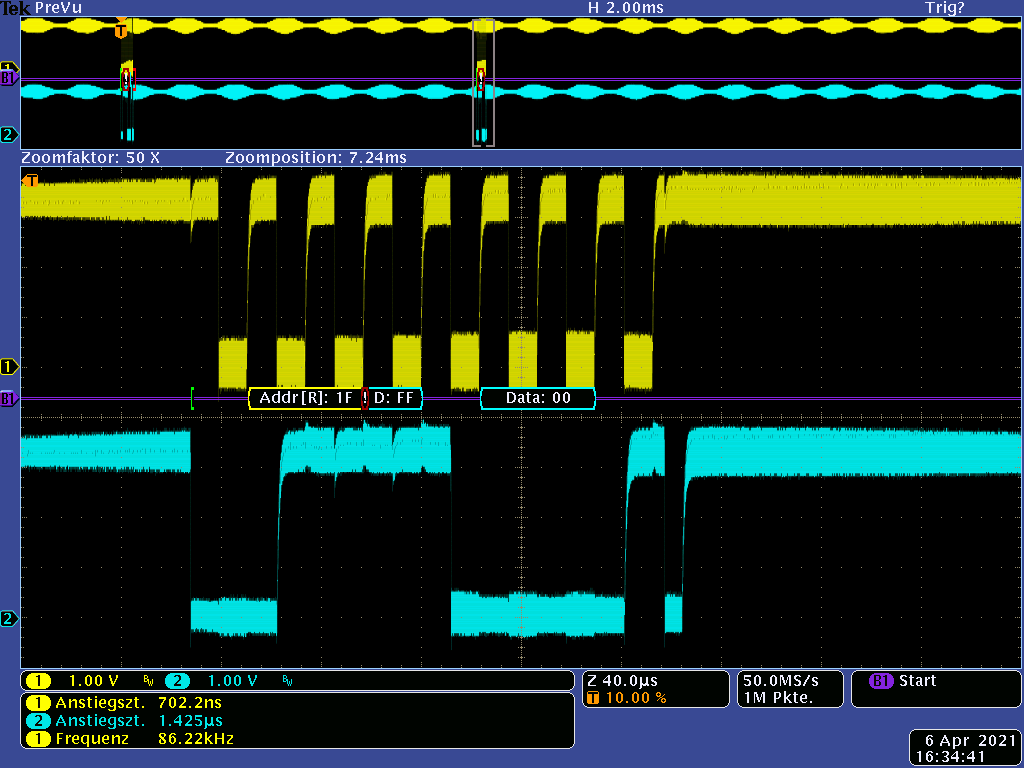

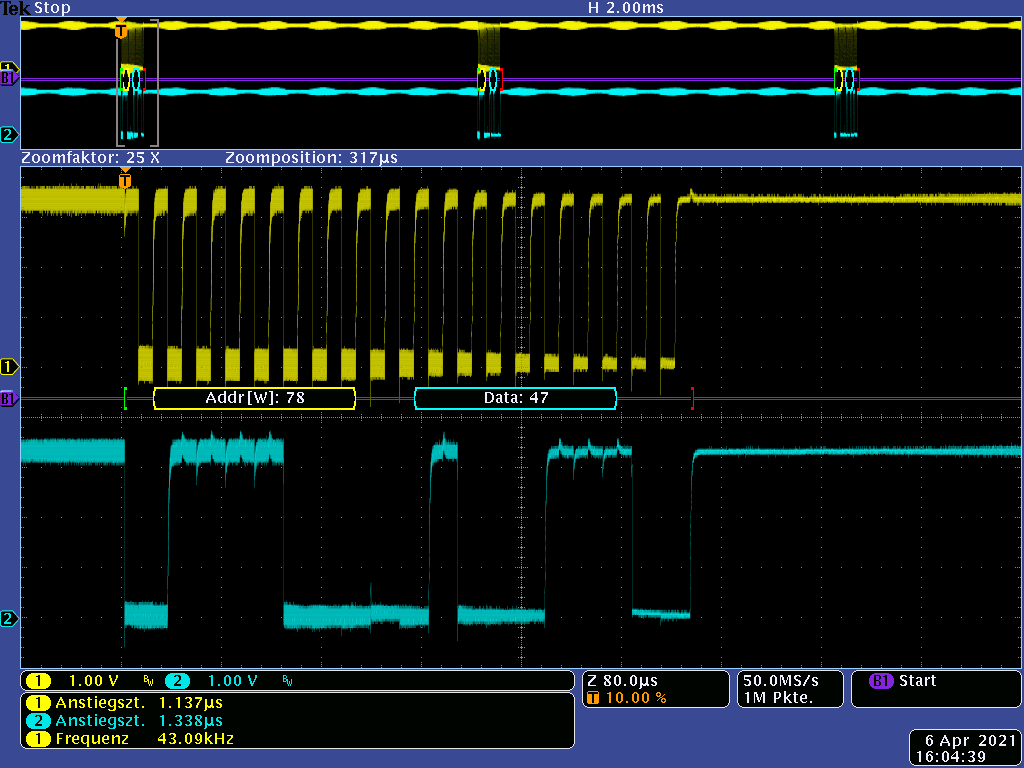

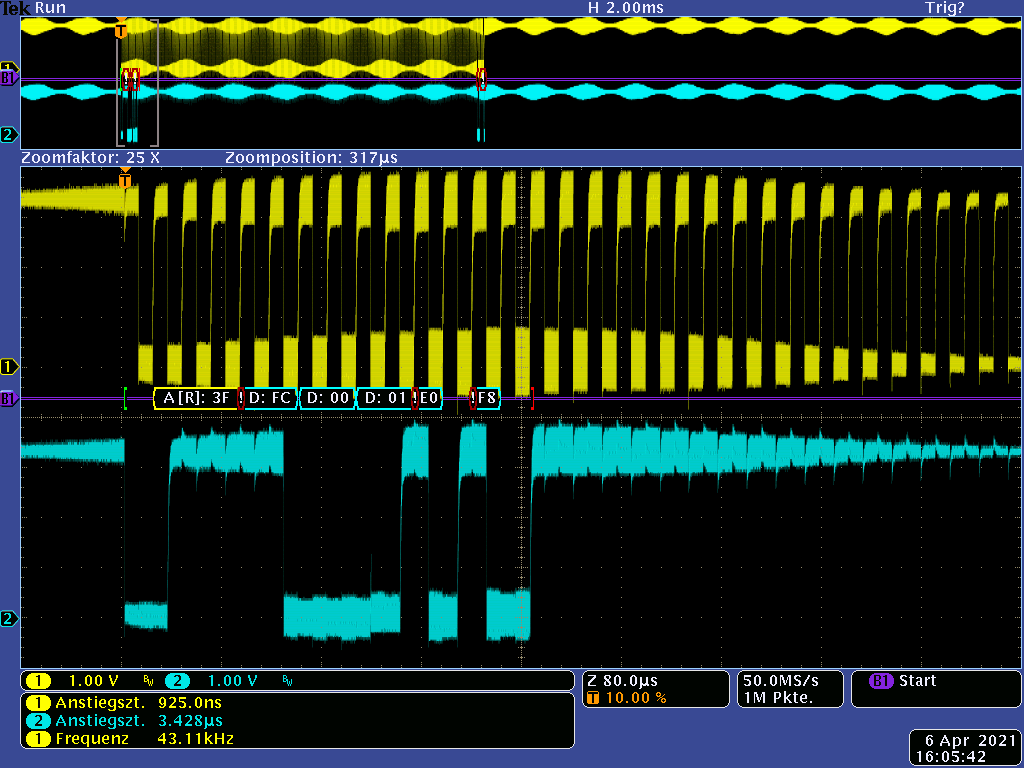

此外、我们还观察到(下一个图像)、即使射频暴露已结束、计时也会继续进行。

- SDA 一直为高电平。 可以看到大约20个时钟。 这些必须来自 USCI!

- 为什么 USCI 不会停止? 因为在8个时钟和一个 NACK 之后、USCI 应保持静止。

- USCI 如何进入该状态?

我们期待您的答复。

谢谢。

<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<< 第一个帖子的结尾 >>>>>>>>>>>>

第3个帖子的附加内容:

-使用 ACK 寻址0x78看起来是正确的。

-使用 ACK 寻址0x78看起来是正确的。