主题中讨论的其他器件: EVM430-FR6043

大家好、

以下是客户可能需要您帮助的一些问题:

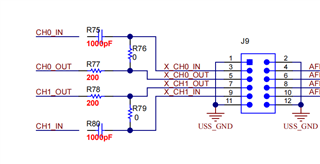

公司计划使用 msp430fr6043设计水表。 我们已 修改图1中 EVM430-FR6043上的电容和电阻。 我们使用了 msp430fr6043的代码示例、该示例名为 msp430fr6043_saph_01.c、然后发布这些代码。 我们使用示波器来查看 CH0_OUT 引脚的波形、如图2、3所示。 我们面临的问题是、示波器波形不是方波、我们怀疑它不是激励信号。 我们希望先生成激励信号、但我们不知道这有什么问题、请告知我们、非常感谢!

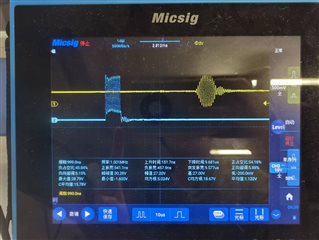

图1.

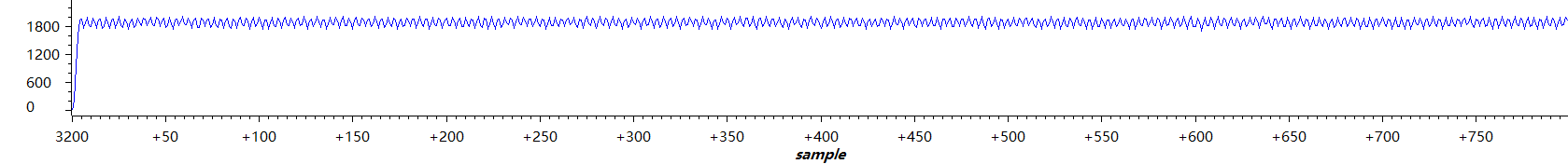

图2.

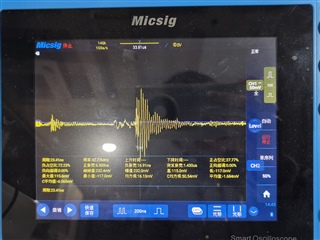

图3.

msp430fr6043_saph_01.c

#include <msp430.h>

#define OSCTYPE__CRYSTAL OSCTYPE_0

void HSPLL_init(void);

int main(void)

{

WDTCTL = WDTPW | WDTHOLD; // Stop WDT

// Configure P1.5 as output for LED

P1OUT &= ~BIT5;

P1DIR |= BIT5;

// Disable the GPIO power-on default high-impedance mode to activate

// previously configured port settings

PM5CTL0 &= ~LOCKLPM5;

// Clock System Setup

CSCTL0_H = CSKEY_H; // Unlock CS registers

CSCTL1 = DCOFSEL_3 | DCORSEL; // Set DCO to 8MHz

// Set SMCLK = MCLK = DCO, ACLK = VLOCLK

CSCTL2 = SELA__VLOCLK | SELS__DCOCLK | SELM__DCOCLK;

CSCTL3 = DIVA__1 | DIVS__8 | DIVM__8; // MCLK = SMCLK = 1MHz

CSCTL0_H = 0; // Lock CS registers

HSPLL_init(); // Initialize the HSPLL and wait for it to lock

// Set up the PPG settings

SAPHKEY = KEY; // Unlock the SAPH registers

SAPHPGC = PLEV_0 | PPOL_0 | 0x000A; // 10 excitation pulses, 0 stop pulses, output low when inactive, high polarity

SAPHPGLPER = 40; // Low phase = 40 HSPLL cycles = 500ns

SAPHPGHPER = 40; // High phase = 40 HSPLL cycles = 500ns

SAPHPGCTL = TRSEL_2 | PPGCHSEL_0 | PGSEL_0; // TA2.1 trigger, CH0 output, register mode

// Set up the PHY to output PPG on dedicated CH0_OUT pin

SAPHOSEL = PCH0SEL__PPGSE; // Output PPG

// Enable the PPG

SAPHPGCTL |= PPGEN;

// Configure TA2.1 for ~1/sec to trigger the pulse generation and toggle LED

TA2CCR0 = 9400;

TA2CCR1 = 4700;

TA2CCTL1 = OUTMOD_7 | CCIE; // Enable output signal to trigger PPG, enable Interrupt

TA2CTL = TASSEL__ACLK | TACLR | MC__UP; // Timer sourced from ACLK (VLO), clear timer

while(1)

{

__bis_SR_register(LPM0_bits | GIE); // Enter LPM3 w/interrupt

__no_operation(); // For debug

}

}

// Timer A2 interrupt service routine

#if defined(__TI_COMPILER_VERSION__) || defined(__IAR_SYSTEMS_ICC__)

#pragma vector = TIMER2_A1_VECTOR

__interrupt void Timer2_A1_ISR(void)

#elif defined(__GNUC__)

void __attribute__ ((interrupt(TIMER2_A1_VECTOR))) Timer2_A1_ISR (void)

#else

#error Compiler not supported!

#endif

{

switch(__even_in_range(TA2IV, TAIV__TAIFG))

{

case TAIV__NONE: break; // No interrupt

case TAIV__TACCR1:

P1OUT ^= BIT5; // Toggle LED to show new cycle

break;

case TAIV__TAIFG: break; // overflow

default: break;

}

}

void HSPLL_init(void)

{

// Configure USSXT Oscillator

HSPLLUSSXTLCTL = OSCTYPE__CRYSTAL | USSXTEN;

// Set up timer to wait in LPM for crystal stabilization time = 4096 clocks for crystal resonator.

// For 8MHz XTAL, 4096 clocks = 512us. Using VLO = 9.4kHz, wait 5 timer clock cycles = 532us.

TA4CCR0 = 5;

TA4CCTL0 = CCIE; // Enable Interrupt

TA4CTL = TASSEL__ACLK | TACLR | MC__UP; // Timer sourced from ACLK (VLO), clear timer

__bis_SR_register(LPM3_bits | GIE); // Enter LPM3 w/interrupt

__no_operation(); // For debug

// Check if oscillator is stable

while((HSPLLUSSXTLCTL & OSCSTATE) == 0);

// Output oscillator on pin

HSPLLUSSXTLCTL &= ~XTOUTOFF;

// Init PLL

// Use the PLLM setting to get 80MHz output from our 8MHz input

// Equation: PLL output clock frequency x 2 = input clock frequency x (PLLM+1)

// Input clock frequency = 8MHz

// Desired PLL output clock frequency = 80MHz

// PLLM = 19

HSPLLCTL = PLLM4 | PLLM1 | PLLM0 | PLLINFREQ; //PLLM = 19, PLL input frequency > 6MHz

// Power up the UUPS to start the PLL

UUPSCTL |= USSPWRUP;

// Wait for UUPS to power up

while((UUPSCTL & UPSTATE_3) != UPSTATE_3);

// Wait for PLL to lock

while(!(HSPLLCTL & PLL_LOCK));

}

// Timer A4 interrupt service routine

#if defined(__TI_COMPILER_VERSION__) || defined(__IAR_SYSTEMS_ICC__)

#pragma vector = TIMER4_A0_VECTOR

__interrupt void Timer4_A0_ISR(void)

#elif defined(__GNUC__)

void __attribute__ ((interrupt(TIMER4_A0_VECTOR))) Timer4_A0_ISR (void)

#else

#error Compiler not supported!

#endif

{

// Stop the timer and wake from LPM

TA4CTL = MC__STOP;

__bic_SR_register_on_exit(LPM3_bits | GIE);

__no_operation();

}

--

谢谢、此致

耶鲁