您好!

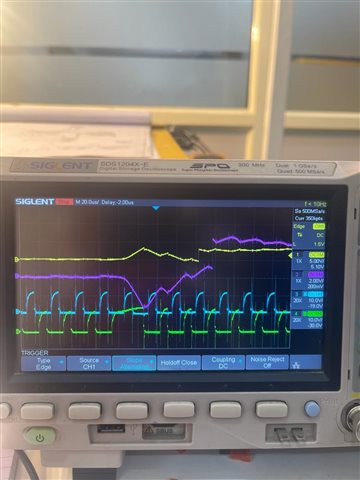

我使用 msp430fr2355进行以下设置。 使用2个 PWM。 其中一个在一段时间后打开100%占空比并导致抖动(如所附波形所示。

void PWM_init (void)

{

PM5CTL0 &=~μ A LOCKLPM5;

TB1CCR0 = 400-1;// PWM 周期

TB1CCTL1 = OUTMOD_7;//| CCIE;// CCR1复位/置位

TB1CTL = TBSSEL__SMCLK | MC__UP | TBCLR;//| TBIE;// SMCLK、向上计数模式、清除 TBR

_delay_cycles (180);

TB3CCR0 = 400-1;// PWM 周期

TB3CCTL5 = OUTMOD_7;

TB3CTL = TBSSEL__SMCLK | MC__UP | TBCLR;

}

请帮助解决此问题。

谢谢。

锡瓦拉詹