主题中讨论的其他器件:MSPM0G3507

大家好、

使用 MSPM0G3507 (Launchpad)时、我们将尝试在16MHz 下对 SYSOSC 应用微调、然后应用 PLL 以达到80MHz。

但面对一些问题、有时在应用 PLL 时 SYOSC 会恢复到32MHz、而在其他时候、CPUCLK 不是80MHz。

如果没有修整、PLL 可以正常使用。

您能为我们建议后续步骤吗?

此致、

马德赫里亚

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

使用 MSPM0G3507 (Launchpad)时、我们将尝试在16MHz 下对 SYSOSC 应用微调、然后应用 PLL 以达到80MHz。

但面对一些问题、有时在应用 PLL 时 SYOSC 会恢复到32MHz、而在其他时候、CPUCLK 不是80MHz。

如果没有修整、PLL 可以正常使用。

您能为我们建议后续步骤吗?

此致、

马德赫里亚

我在 SLAU846a 2.3.1.2.4下在 SYSOSC 上以16MHz 进行了校准、同时禁用了 PLL。 应用修整值时、无需复位 MCU、也无需重置 MCU 即可测量相同的值。 我在配置之后执行了校准、就像 测试1.

测试1:

即使 在 MCU 复位后、也使用 ENABLE_USE_PLL = 0、FCL_ENABLED = 1、FCL_PREVE = 1、测量结果为16.05Mhz。

测试2:

使用 ENABLE_USE_PLL = 0、 FCL_ENABLED = 1、 FCL_PERIOD = 0、 在复位前和复位后测量32MHz MCU 15.0Mhz。

测试3:

使用 ENABLE_USE_PLL = 1、 FCL_ENABLED = 1、 FCL_PERIOD = 1时、我的测量值为32.4Mhz、 即使 在 MCU 复位后也是如此。 这是按照关于 slau846a SYSPLL 使用示例(第114页) 的建议和使用 CLK_OUT 且启用频率校正环路(FCL)(存在 ROSC 电阻器)的调整过程(第111页)进行的。 这是我认为应用修整和 PLL 的正确方法、但结果并非预期结果。

测试4:

通过使用 ENABLE_USE_PLL = 1、FCL_ENABLED = 1 、FCL_PAYER = 0、我应用时的测量值为32.4Mhz、 但 在复位后、MCU 更改为15.0Mhz、与 测试2 。

按照我的测试代码:

/*

* Copyright (c) 2023, Texas Instruments Incorporated

* All rights reserved.

*

* Redistribution and use in source and binary forms, with or without

* modification, are permitted provided that the following conditions

* are met:

*

* * Redistributions of source code must retain the above copyright

* notice, this list of conditions and the following disclaimer.

*

* * Redistributions in binary form must reproduce the above copyright

* notice, this list of conditions and the following disclaimer in the

* documentation and/or other materials provided with the distribution.

*

* * Neither the name of Texas Instruments Incorporated nor the names of

* its contributors may be used to endorse or promote products derived

* from this software without specific prior written permission.

*

* THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS"

* AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO,

* THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR

* PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT OWNER OR

* CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL,

* EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO,

* PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS;

* OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY,

* WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR

* OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE,

* EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

*/

#include "ti_msp_dl_config.h"

volatile uint32_t mSysCTL = 0x0000000;

#define POWER_STARTUP_DELAY (16)

#define GPIO_CLKOUT_PORT GPIOA

#define GPIO_CLKOUT_PIN DL_GPIO_PIN_14

#define GPIO_CLKOUT_IOMUX (IOMUX_PINCM36)

#define GPIO_CLKOUT_IOMUX_FUNC IOMUX_PINCM36_PF_SYSCTL_CLK_OUT

#define GPIO_ROSC_PORT GPIOA

#define GPIO_ROSC_PIN DL_GPIO_PIN_2

#define GPIO_ROSC_IOMUX (IOMUX_PINCM7)

#define CPUCLK_FREQ 32000000

#define ENABLE_USE_PLL 1 // 0 - DISABLE / 1 - ENABLE

#define FCL_ENABLED 1 // 0 - DISABLE / 1 - ENABLE

#define FCL_BEFORE 1 // 0 - AFTER / 1 - BEFORE

void mySysInit()

{

DL_GPIO_reset(GPIOA);

DL_GPIO_reset(GPIOB);

DL_GPIO_enablePower(GPIOA);

DL_GPIO_enablePower(GPIOB);

delay_cycles(POWER_STARTUP_DELAY);

DL_GPIO_initPeripheralOutputFunction(GPIO_CLKOUT_IOMUX, GPIO_CLKOUT_IOMUX_FUNC);

DL_GPIO_enableOutput(GPIO_CLKOUT_PORT, GPIO_CLKOUT_PIN);

DL_GPIO_initPeripheralAnalogFunction(GPIO_ROSC_IOMUX);

DL_SYSCTL_setSYSOSCFreq(DL_SYSCTL_SYSOSC_FREQ_BASE);

/* Set default configuration */

DL_SYSCTL_disableHFXT();

DL_SYSCTL_disableSYSPLL();

//DL_SYSCTL_enableExternalClock(DL_SYSCTL_CLK_OUT_SOURCE_SYSPLLOUT1,

// DL_SYSCTL_CLK_OUT_DIVIDE_2);

DL_SYSCTL_enableExternalClock(DL_SYSCTL_CLK_OUT_SOURCE_SYSOSC,

DL_SYSCTL_CLK_OUT_DIVIDE_DISABLE);

//Low Power Mode is configured to be SLEEP0

DL_SYSCTL_setBORThreshold(DL_SYSCTL_BOR_THRESHOLD_LEVEL_0);

}

int main(void)

{

//SYSCFG_DL_init();

mySysInit();

#if (FCL_ENABLED == 1 && FCL_BEFORE == 1)

// Need to be at FREQ_BASE

DL_SYSCTL_enableSYSOSCFCL();

#endif

/**

* FCL Disabled

* RDIV 0x150

* FINE 0x08

* COARSE 0x13

* CAP 0x01

*

* FCL Enabled

* RDIV 0x150

* FINE 0x08

* COARSE 0x13

* CAP 0x01

*/

DL_SYSCTL_SYSOSCUserTrimConfig myTrim =

{

0x150, // RDIV

0x08, // resistorFine

0x15, // resistorCoarse

0x01, // capacitor

DL_SYSCTL_SYSOSC_USERTRIM_FREQ_16M

}; //Trim Config

DL_SYSCTL_configSYSOSCUserTrim(&myTrim); //Writing the SYSOSC User Register

DL_SYSCTL_setSYSOSCFreq(DL_SYSCTL_SYSOSC_FREQ_USERTRIM); //Updating the SYSOSC Frequency to User Value

/*WOTHOUT ROSC END*/

#if (FCL_ENABLED == 1 && FCL_BEFORE == 0)

/*WITH ROSC START*/

DL_SYSCTL_setSYSOSCFreq(DL_SYSCTL_SYSOSC_FREQ_BASE); // changing the SYSOSC to Base i.e. 32MHz

DL_SYSCTL_enableSYSOSCFCL(); // Enabling the FCL

DL_SYSCTL_setSYSOSCFreq(DL_SYSCTL_SYSOSC_FREQ_USERTRIM); // Changing to trim value frequency

#endif

#if (ENABLE_USE_PLL == 1)

static const DL_SYSCTL_SYSPLLConfig gSYSPLLConfig = {

.inputFreq = DL_SYSCTL_SYSPLL_INPUT_FREQ_16_32_MHZ,

.rDivClk2x = 3,

.rDivClk1 = 1,

.rDivClk0 = 0,

.enableCLK2x = DL_SYSCTL_SYSPLL_CLK2X_ENABLE,

.enableCLK1 = DL_SYSCTL_SYSPLL_CLK1_ENABLE,

.enableCLK0 = DL_SYSCTL_SYSPLL_CLK0_DISABLE,

.sysPLLMCLK = DL_SYSCTL_SYSPLL_MCLK_CLK2X,

.sysPLLRef = DL_SYSCTL_SYSPLL_REF_SYSOSC,

.qDiv = 9,

.pDiv = DL_SYSCTL_SYSPLL_PDIV_2,

};

DL_SYSCTL_setSYSOSCFreq(DL_SYSCTL_SYSOSC_FREQ_BASE);

DL_SYSCTL_configSYSPLL((DL_SYSCTL_SYSPLLConfig *) &gSYSPLLConfig);

DL_SYSCTL_setULPCLKDivider(DL_SYSCTL_ULPCLK_DIV_2);

while((DL_SYSCTL_getClockStatus() & DL_SYSCTL_CLK_STATUS_SYSPLL_GOOD) != DL_SYSCTL_CLK_STATUS_SYSPLL_GOOD);

DL_SYSCTL_setMCLKSource(SYSOSC, HSCLK, DL_SYSCTL_HSCLK_SOURCE_SYSPLL);

DL_SYSCTL_setMCLKDivider(DL_SYSCTL_MCLK_DIVIDER_DISABLE);

DL_SYSCTL_setSYSOSCFreq(DL_SYSCTL_SYSOSC_FREQ_USERTRIM);

#endif

while (1) {

mSysCTL = SYSCTL->SOCLOCK.SYSOSCFCLCTL;

}

}

由于我们将在不同的值中使用 PLL、但主要是在80MHz 频率下使用、我们应该在启用 PLL 的情况下查看最终值、还是应该在禁用 PLL 但查看 SYSOSC 用户值的情况下执行校准、如16MHz? 由于我们计划在 PLL 中使用不同的时钟频率、因此至少要使用两种时钟频率(80MHz 及其他更低频率以适应低功耗模式下的电流消耗)

3-我们是否需要在每次更改修整值时执行复位以检查时钟? 我们正在考虑建立一个可以自动校准的功能、但对每一项更改进行复位会更困难。

4 -要应用 PLL、参考手册中提到我们需要在应用 PLL 之前更改为 FREQ BASE、但由于我们计划使用16MHz FREQ 用户、因此 PLL 参数不同。 因此、如果我们将使用16MHz 的 PLL 并使用80MHz、当我们应用 PLL 时、我们使用直接显示到最终值的值、或者我们应该应用一些逻辑值、思考如何32MHz、然后在应用 FREQ 用户之后我们更改 PLL 值? 这在参考手册上有点模糊。

您好,Ulysses,

您能否在时钟输出信号上添加分频器?

此致、

卢克

Luke、您好!

是的、我将使用分频器2重新运行测试。

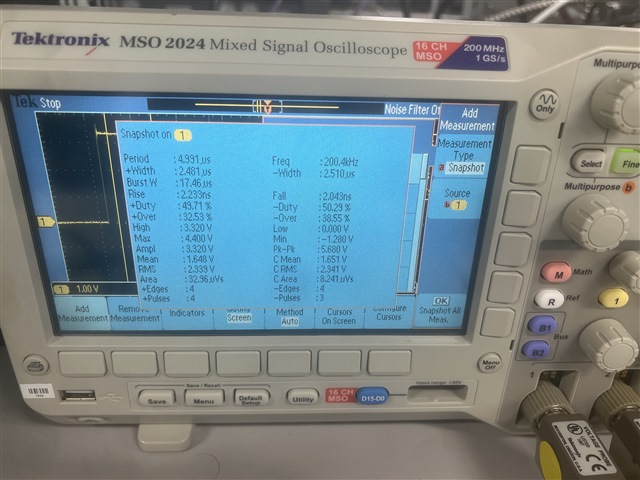

1.同意您的意见,这是我在所有测试中看到的信号,但我没有任何连接,是引脚(A14)直接到示波器。 我正在使用 A14引脚上的 Launchpad mspm0g3507时钟输出。 我正在使用示波器100Mhz 1GSa/s。

2.好的,就是我所期望的,只需要检查一下

3. A.相关知识

B.我对此很感兴趣。 我们可能会使用它、

4.让我知道更多关于这一点,因为这对我来说有点困惑

您好,Ulysses,

我创建了一个计时器示例、该示例将根据 SYSPLL 的实际频率获得更高精度的计时器。

如果您有任何后续问题、请告诉我。

e2e.ti.com/.../timer_5F00_higher_5F00_accuracy_5F00_example.zip

此致、

卢克