主题中讨论的其他器件: MSP430FR2476

专家们、您好!

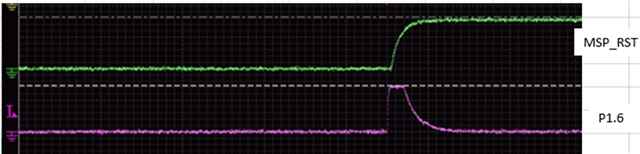

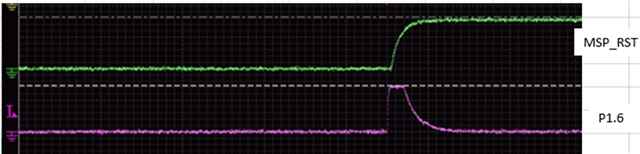

我的客户现在正在评估 MSP430FR2475。 MSP430FR2475安装在客户电路板上。 客户报告、6引脚在释放 RESET 后经过一段时间(~100us)变为"高电平"。 此行为是否正常? 如果不是、您是否会告诉客户应检查哪些地方? 该引脚在外部下拉(470k Ω)。

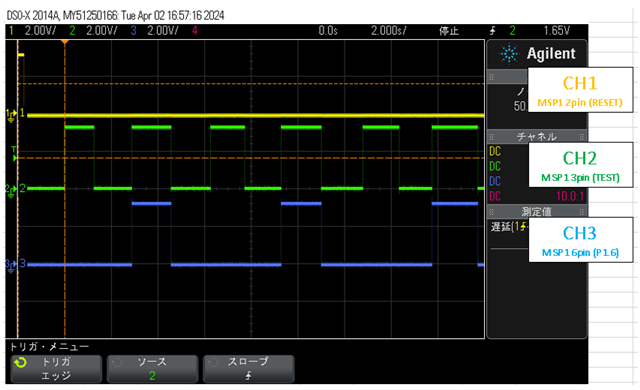

电压:2.0V/div

时间:200us/div

此致、

藤原市

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

专家们、您好!

我的客户现在正在评估 MSP430FR2475。 MSP430FR2475安装在客户电路板上。 客户报告、6引脚在释放 RESET 后经过一段时间(~100us)变为"高电平"。 此行为是否正常? 如果不是、您是否会告诉客户应检查哪些地方? 该引脚在外部下拉(470k Ω)。

电压:2.0V/div

时间:200us/div

此致、

藤原市

您好、 Yasushi

尊敬的 Helic:

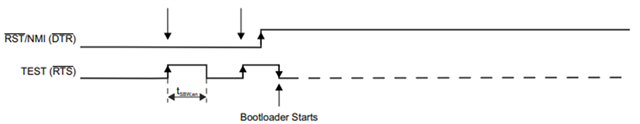

客户想要做的是从外部 MPU 向 MSP430发送 TEST 和 RST 信号、以将 MSP430置于 BSL 模式。

以下信号序列从外部 MPU 发送。

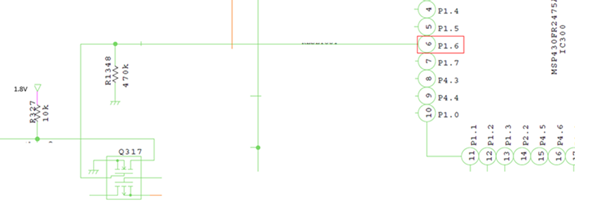

但是、在测试信号的第二个高电平输出后、会从端口1.6引脚输出一个高电平信号、并且未在当前电路配置中进入 BSL 模式。 此外、该1.6引脚没有外部上拉电路配置。

[问题]

我们已经查看了 MSP430数据表、有一件事需要关注。 当 TEST 信号变为高电平时、MSP 内的 JTAG 功能将被激活、并在内部上拉1.6引脚。 客户理解是否正确?

此致、

藤原市

您好、 Yasushi

很抱歉我迟到了。

在过去的几天里、我没有收到该主题的 E2E 电子邮件通知。

我将再次调查这个问题~

[报价 userid="36167" url="~/support/microcontrollers/msp-low-power-microcontrollers-group/msp430/f/msp-low-power-microcontroller-forum/1325357/msp430fr2475-6-pin-behavior-after-releasing-reset/5073698 #5073698"][question]引导加载程序在测试信号的下降沿启动。 但是、如果禁用了 BSL、引导加载程序序列将允许器件进入 JTAG 模式。 (在图中、您发送2.3存储器编程控制序列案例2b。)。

TCLK 和 P1.6是同一引脚、但我仍然认为这不是正常的。

——

客户可以在没有外部电路的情况下对 MSP430进行一些测试、以确认这是 MSP430的内部问题吗?

此致、

Helic

您好、 Yasushi

1. 客户是否在 无程序的芯片上进行了测试(空芯片)? 效率和热性能。

2.有多少个芯片出现这个问题? 客户测试了多少款芯片? 测试结果是什么?

3. 如果仍然有问题、我会同时在 TI 实验室中进行测试。 我将尝试重现这种 P1.6上拉现象。

由于采用 JTAG 操作、输入测试信号时是否上拉端口1.6

我需要测试、但我认为这是异常的。

此致、

Helic

尊敬的 Helic:

客户确认了您的问题。

1. 客户已使用评估板 LP MSP430FR2476进行验证。

P1.6端口与 TEST 信号同步变为低电平/高电平。 它似乎是对第二个高电平测试信号做出响应。 下图显示了观察到的波形。 请验证这一现象。

2.客户检查过这种现象:

-一个 EVM

-两个客户板

[问题]

客户想知道 MSP430微控制器的规格。

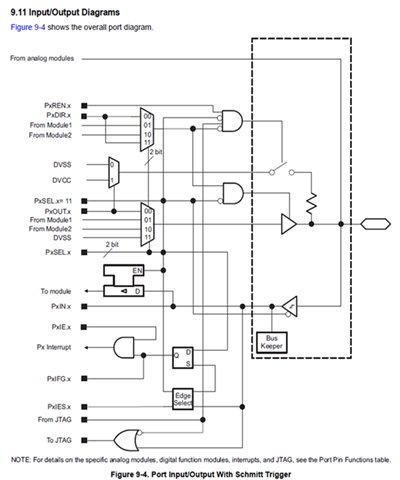

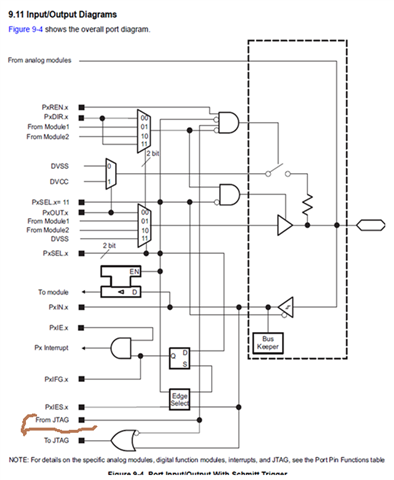

在下面的方框图中、用于控制上拉/下拉的 FROM JTAG (红色标记)布线的规格是什么?

尊敬的 Yasushi、

很抱歉稍后回复。 这是我们设计团队的回应

对于该器件、使用了由 JTAG 逻辑中的 TEST 引脚计时的下降触发器和上升触发器、这将进行 SBW/4线制 JTAG/BSL 解码。 此器件在最后一个 TEST 低电平-高电平转换期间进入4线制 JTAG 模式、并在 TEST 引脚被降低后返回到 BSL 进入状态。 因此、P1.6上的拉高与4线制 JTAG 相关并且与 BSL 无关。 BSL 将在降低 TEST 引脚后启动。