Other Parts Discussed in Thread: MSP430FR2475, MSP430FR2476

主题中讨论的其他器件: MSP430FR2476

专家们、您好!

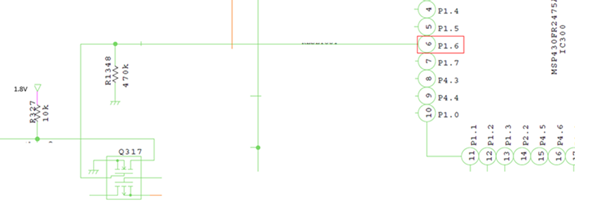

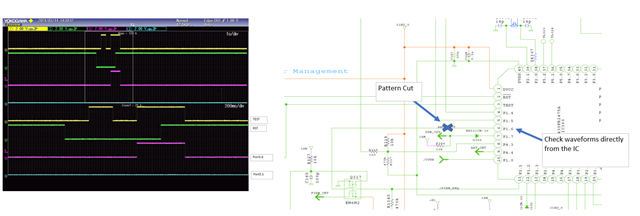

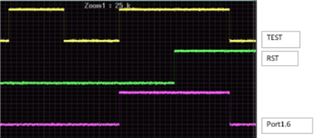

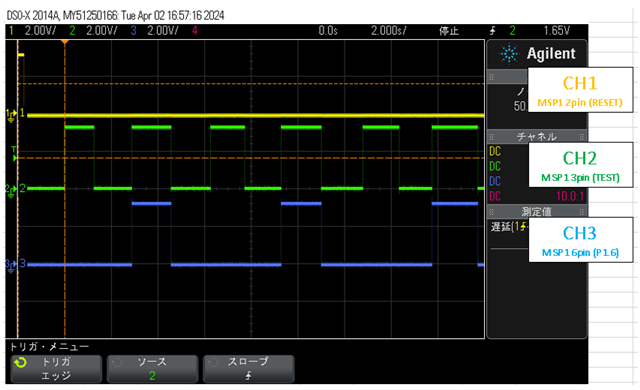

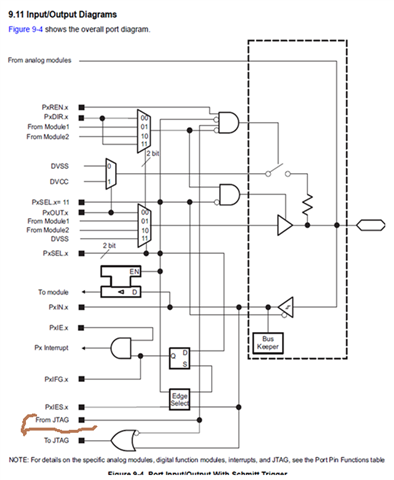

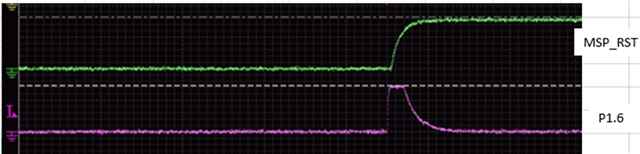

我的客户现在正在评估 MSP430FR2475。 MSP430FR2475安装在客户电路板上。 客户报告、6引脚在释放 RESET 后经过一段时间(~100us)变为"高电平"。 此行为是否正常? 如果不是、您是否会告诉客户应检查哪些地方? 该引脚在外部下拉(470k Ω)。

电压:2.0V/div

时间:200us/div

此致、

藤原市