工具与软件:

嗨、团队:

我的客户正在开发 MSP430F67761IP FW。 下面列出了一些问题。 请帮助您澄清。 谢谢你。

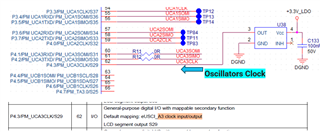

- 客户了解到 MSP430F67761无法在外部提供准确的25MHz HFXT。 客户想知道他们是否需要 更精确的时钟、是否可以通过"P4.3/PM_UCA3CLK/S29"馈送振荡器时钟?

- 如果问题1是"是"、那么软件中需要设置什么设置?

下面列出了有关 MCLK 和5MHz UART 的其他问题

3.如果这个 MCU 时钟采用 DCO 结构、那么他们应该设置哪些寄存器来使 MCLK 以最高的内部频率运行?

如何设置 eUSCI (UART 模式)来支持5MHz (UART 模式)比特率?