主题中讨论的其他器件:UCC28C55、

工具与软件:

我有一个基于 Webench 的隔离式24Vin/250Vout 直流/直流设计(参数如下所示)和 PDF attached.e2e.ti.com/.../_2800_TI-Webench_2900_-24Vin_2C00_-250Vout-_2800_25W_2900_-iso-boost-converter-design-_5F00_090624.pdf

WEBENCH设计报告

设计:59 UCC28C55QDRQ1

UCC28C55QDRQ1 22V-26V 至250.00V @ 0.1A

VinMin = 22.0V

VinMax = 26.0V

VOUT = 250.0V

Iout = 0.1A

器件= UCC28C55QDRQ1

拓扑=反激式

已创建= 2024年09月06日12:45:08.673

BOM 成本=不适用

BOM 数量= 39

总 Pd = 3.35W

数据表显示了两(2)个应用示例、两个示例都是从控制次级(辅助)绕组断开的两(2)个二极管、其反馈网络和启动路径由阻断二极管隔离。 Webench 设计中未包含第二个(阻塞)二极管、这可能是我看到的问题的根本原因。

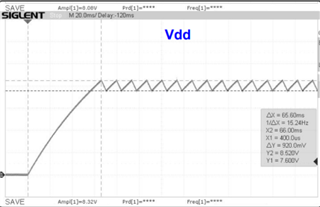

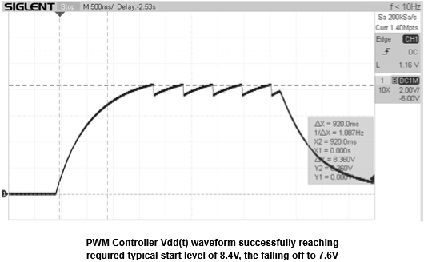

监控示波器上的 VDD (t)-28C55-VDD 引脚-原始设计将斜升(充电)至大约4V。 提高启动电流(降低 Rstart)-(24-8.4V)/Rstart -我改善了 Vdd (t)的情况。 在对 Itart 进行第一组更改后、Vdd (t)将上升到8.4V、大概是启动时、它会将 Cboot//CVDD 消耗至7.6V 电平... UVLO? 器件关断、然后斜升至8.4V、再次下降、并且重复此循环。 数据表建议可能需要1300uA 至2000uA 的启动电流、这似乎与 Webench Istart 的可用电流低于200uA (24V-8.4V)/82.4K 欧姆相矛盾。

随着 Istart 的进一步增加和 Rfbt 的增加、Rfbb 电阻器的增加--为了使 Vdd 节点的负载最小化--我能够启动芯片、通过观察到稳定的 VREF = 5V 输出来验证(部分)。

我的设计在 Rfbb 和 chip-FB 之间插入一个电位器(Rpot)电阻、这有助于故障排除不同 RFB (总计)值对 Vdd 的影响。 这种测试方法是仅用于排除启动故障的方法。 由于次级绕组(辅助绕组、sec2绕组)尚未连接、因此必须使用合理的 Rfbt、Rfbb 比值、而不增加 Rpot 电阻、以达到11.5至12V 的额定 Vdd。 只添加 RPOT 电阻是不可行的。

因此、我需要28C55专家的帮助来为我当前(基于 Webench)的设计修补解决方案、然后后续的设计修订版可以捕获此对话框中可能出现的任何增强、更正和改进。

非常感谢您的支持。

Steve

纽约