工具与软件:

你(们)好

我们正在使用 TPS543C20ARVFR 为 VCCINIT 0.85V (用于 Zynq Ultrascale + XQZU19EG-2FFQB1517I)供电。我们已针对0.85V 39A 对其进行设计。 当未连接负载时、降压输出为0.846V。我们隔离了负载、就像我们提供了0欧姆隔离电阻器一样。但当 连接负载(FPGA)时、电压会降至0.786V。 该电源轨上的阻抗为1.5欧姆。 请告诉我们可能出现了什么问题。

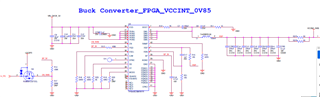

以下是降压转换器的原理图。 同样、下面是用于 FPGA 的 VCCINIT 电源轨的去耦电容器。 在 FPGA 上、此电压轨也几乎没有钽电容器。 这可能是任何问题。 通过 PI 仿真验证了布局、并确保平面的压降容差不超过3%。