工具与软件:

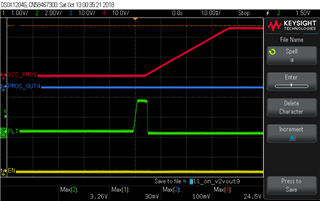

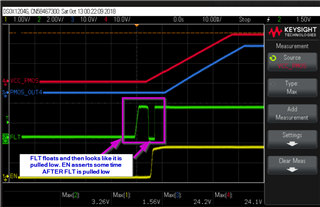

我的 TPS16413在启动时给我带来麻烦。 似乎在某些情况下、我们会在不应引起故障的情况下看到 FLT。 我们会在启动时将 EN 引脚驱动为高电平以驱动固件中的负载、但我注意到有一段时间后、FLT 被置为有效。

故障的可能条件:

- 过流(大于1A 拉)

- 我们在设计中绘制< 250mA 的整体图、这是不可能的。

- 热关断(器件的 T_Junction > 155°C)

- 运行时没有可见的温度、不应该是这个温度。

- 过压(OVP 引脚电压上升至超过1.53V)

- OVP 引脚电压看起来是1.24ish 伏...这应该是可以的、我们有一个可将24V 降至1.24V 的1:20分压器

根据我的估计、仅当 VCC_PMOS 跃升到29/30V 时、OVP 才会起作用。

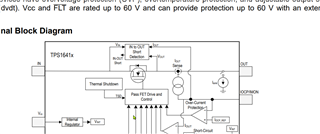

- 输入至输出短路检测

- 可能是罪魁祸首? 也许?

- R_SHORT 是一个电阻器、用于在内部测量30mΩ 最大值以检测输入短路。

- 我非常不清楚我应该测量哪些条件来确认输入到输出短路、以及控制逻辑做出哪些决策来确定是否存在故障。

- 如果 TPS16413在 IN 和 OUT 引脚之间检测到的 R_SHORT 更短、FLT 将被置为低电平。 启动时、FLT 保持低电平。 如果未检测到短路、FLT 会置为无效(高电平)、内部 FET 导通、并传递电流。

- 我们一定不能满足其中一个要求、当我们尝试驱动负载时、电子保险丝与负载对抗。

- 要复位锁存器、必须切换电子保险丝 EN/SHDN 引脚或对 V_CC 电源进行下电上电

- 将 EN/SHDN 引脚保持为低电平>24ms、然后将其驱动为高电平。

我不是很清楚我们是如何违反任何这些条件的。 我在这里遗漏了什么?

此外、当禁用时、似乎电子保险丝正在尝试驱动施加的24V 负载。 当 EN 被拉至低电平时、如果我在 OUT 引脚上施加24V 电压(此网络上的另一个电路将读取24V 信号、但我希望电子保险丝不会干扰)、电子保险丝的预期行为是什么? 现在、我看到 OUT 引脚在断电时从24V 变为上电时的8V。 我已将其隔离回此器件、所以肯定是错开了电路。