工具与软件:

有许多600V 半桥栅极驱动器采用8引脚 SOIC 封装和更多引脚数的14引脚封装。 使用8引脚 SOIC 封装时、由于引脚数受限、仅基本的半桥栅极驱动器功能可用、并且所有8个引脚驱动器都有一个接地基准引脚。 采用14引脚及更多引脚数的 SOIC 封装、可以通过一些引脚来实现其他功能、包括用于控制信号的接地基准引脚和用于低侧驱动器接地基准的单独接地基准引脚。

分离栅极驱动器接地对于优化控制和驱动器接地布局具有诸多优势。 在大多数应用中、功率级接地(即低侧 MOSFET 源极连接)中会出现接地反弹。 低侧 MOSFET 源极与输入电容器负极端子之间存在寄生电感。 此外、通常还有一个控制接地、该接地通常是以输入电容器负端子为基准的"安静"或低噪声接地。 首先、我将展示使用单个接地驱动器与栅极驱动器接地连接之间的权衡。 然后展示了分离接地功能如何帮助实现驱动器电路的优化布局。

单接地驱动器和分离接地驱动器的利弊:

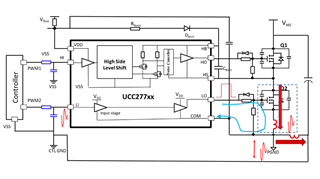

图1显示了连接到低侧 MOSFET 源极的半桥栅极驱动器接地(COM)。 此布局的优势是可最大限度减小低侧栅极驱动环路中的栅极驱动 PCB 布线电感、如蓝线所示。 缺点是在开关事件期间、由于 di/dt 较高、动力总成接地(PGND)和控制接地(CTL GND)之间将存在振铃。 这种振铃可能会出现在 LI 和 HI 输入上、这可以通过 LI 和 HI 驱动器引脚上的 R/C 滤波器来解决。 输入滤波器足以抑制 LI 和 HI 上的振铃、可能会影响控制驱动器输入到驱动器输出信号的延迟。

图1

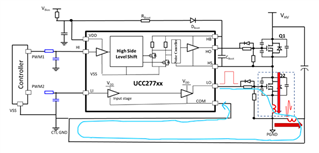

图2显示了连接到控制地(CTL GND)的半桥栅极驱动器接地(COM)。 在这种布局下、低侧栅极驱动环路会变得更长(如蓝线所示)、这将影响 MOSFET VGS 上升和下降时间、从而影响 MOSFET 开关性能。 此布局的优势是可以更大限度地减少驱动器 LI 和 HI 输入引脚上的振铃和噪声。

图2

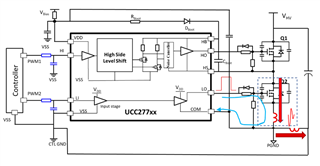

在图3中、显示了一个具有分离接地的栅极驱动器、该驱动器允许将驱动器输入信号(LI 和 HI)以控制接地(CTL GND)为基准、并且将驱动器输出接地(COM)连接到 MOSFET 源极。

图3

通过分离接地栅极驱动器、驱动器的 COM 引脚直接连接到 MOSFET 的源极可最大限度地减小低侧栅极驱动环路电感、并且控制器以 VSS 为基准、有助于防止噪声注入栅极驱动器 LI 和 HI 输入引脚。

分离接地驱动器设计注意事项:

需要考虑使用分离接地来优化栅极驱动器电路设计。 由于单独的接地引脚 COM 和 VSS 之间预计会有很大的布局电感、因此在 VDD 到 VSS 和 VDD 到 COM 之间需要有旁路电容。 这是为了确保从 VDD 到 VSS 的低噪声、以及栅极驱动输出级与旁路电容器具有低电感连接。

此外、COM 和 VSS 之间会出现高频电压尖峰和振铃。 由于 VDD 到 COM 和 VDD 到 VSS 之间会有电容、因此从 COM 到 VSS 的这种振铃可以耦合到 VDD。 需要考虑 VDD 至 VSS 和 VDD 至 COM 电容器的大小、以更大限度地减少耦合到 VDD 的噪声。 VDD 至 COM 电容器值应根据为 MOSFET QG 充电所需的时间来确定大小、类似于确定用于高侧驱动器偏置的自举电容器的大小、而不是过大的电容值。

确定 VDD 到 VSS 和 VDD 到 COM 电容值的基本指导如下。 对于 VDD 至 COM 电容器、唯一的考虑因素是是否能够为 MOSFET QG 充电。 电容值由以下等式给出:

CVDD_COM = QG (total)/ΔVDD μ V

对于 VDD 至 VSS 电容器、建议将该值的大小设置为 VDD 至 COM 电容值的10倍、以尽量减少耦合到 VDD 中的噪声(从 VDD 至 COM 电容器到 COM 电容器以及 COM 引脚上的振铃)。

使用具有分离接地层的半桥栅极驱动器具有诸多优势、以及要实现卓越性能的一些设计注意事项。 主要优势是能够通过栅极驱动器接地基准来优化低侧栅极驱动环路布局、还可以避免驱动器输入引脚上产生噪声。 一些权衡因素是需要一个比8引脚封装更高的引脚数和一个额外的 VDD 旁路电容器。

TI 提供 具有 Spit 接地功能的 UCC27714 600V 半桥栅极驱动器。 如果更加需要较小的8引脚封装、可以选择 UCC27710 和 UCC27712 620V 半桥栅极驱动器。