工具/软件:

您好的团队、

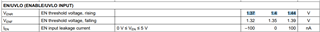

我的客户提到他们发现此设备有一个状态。 EN 电压约为1.47V。 但 Vout 仅为3.3V 至3.6V。 没有完全导通。 将 EN 更改为2V 后、它们可以获得12V 输出

- 我是否可以知道为什么数据表中列出的 VEN 也超过1.44V、但 FET 未完全导通? 我认为这可能是不正常的分配。 请评论我的理解是否正确。

- 另一件事是为什么我们的器件会出现部分时钟? 我以为这是一个很难完全实现的阈值。

谢谢、

Oliver

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好的团队、

我的客户提到他们发现此设备有一个状态。 EN 电压约为1.47V。 但 Vout 仅为3.3V 至3.6V。 没有完全导通。 将 EN 更改为2V 后、它们可以获得12V 输出

谢谢、

Oliver

您好、Oliver:

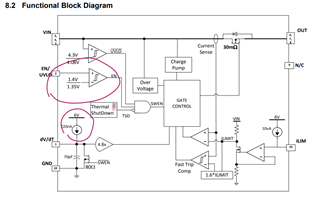

EN 引脚本身不应导致此类行为。 在内部它是比较器的输入、因此电压值不应导致中间输出值。 我看到了中间输出值情况、即 FET 的栅极由于 dVdt 引脚处的一些漏电流而未完全充电。 (在没有适当阻抗的情况下探测此引脚也可能导致其不会上升到完整值)

您能否要求他们提供原理图并检查 DVDT 引脚处是否有漏电路径、或者在检查使能引脚阈值时是否在探测 DVDT 引脚。

此外、这与多个器件/电路板重复。

此致、

Arush