主题中讨论的其他器件: BQSTUDIO、 TIDA-010208

工具/软件:

大家好、TI 员工

我们遇到了一个有趣的问题、我能够在 EVM 板上复制这个问题;下面的详细信息有待重现。

我们为6S 配置了3S 至8S BMS 设计。 我们使用 BQ76952、因为我们熟悉它。 电路板没有 REG1和 REG2电路;BREG 和 REGIN 连接到 VSS。

根据 SLEEPCHG=0降低功耗的建议、我们使用此模式并发运了一些电池包。 客户将其存放了三个月、发现无法输出。 我们计算他们有一个12个月的保质期在睡眠没有充电。

经过大量的头部刮伤,我们已经发现板定期退出睡眠10秒,并返回睡眠,但是,通过这种循环,平均电流是连续睡眠消耗的四倍。 这说明了存储时间的缩短。

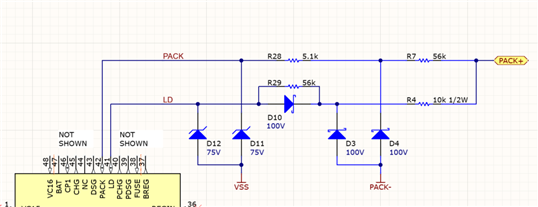

我们可以观察到、由于缺少任何 PACK 引脚负载(或 BMS 中的其他负载)、使用 BQStudio 观察时、PACK 和 LD 检测到的电压会不稳定地跳变。 我们发现、无需太多负载即可保持这些电压稳定并保持睡眠状态。 我有一个旧的 Tektronix TX-3、其输入阻抗为10M Ω、在电池包引脚之间、足够负载。 我通过将其替换为10Mohm 电阻器且 BQ 保持睡眠状态来证明这一点。 我的大部分测试都是使用电路中的 TX-3完成的、这掩盖了问题。

我们想了解的是允许电压上升的机制。 鉴于 CHG FET 体二极管只能将电池组电压保持为极小的值、其他一些电路流可能会将电压"泵浦"得更高、例如 LD 引脚驱动、或 ATE 电路中的泄漏。 这是很难进行外部测量,因为仪表挤压的效果!

若要在 EVM 上复制、请使用如下所示的链接设置6S 并移除 D2。 这会消除 CD 网络上的负载电流、并复制我们没有电路板负载的情况。 将 D2焊盘连接到 BAT+可为 REG 电路(紫线)供电、并且 BMS 正常运行。 加载配置文件并观察 LD 和 PACK 电压跳跃。 这种配置已针对我的 EVM 进行了校准。 如果要在实验中校准电路板、则需要设置 SLEEPCHG=1、以便在电路板稳定时对其进行堆叠、PACK 和 LD 校准。 然后恢复 SLEEPCHG=0并观察电路板定期唤醒并再次睡眠。 在唤醒时间内启用 CHG FET、这将问题范围缩小至 Power:Sleep:Sleep Charger PACK-TOS Delta 和 Power:Sleep:Sleep Charger Voltage Threshold 检测、表明存在充电器并唤醒 BQ。 请参阅:TRM 修订版 B 第67页、最后一段

我们已将 SLEEPCHG=1设置为使客户运行、但如果我们要重新考虑 SLEEPCHG=0、我们需要了解更多信息。

e2e.ti.com/.../6S_5F00_EVM_5F00_pack_5F00_drift_5F00_wakeups.gg.csv