工具/软件:

您好、

我们目前正在调查一个与 UCC28740中的振荡停止行为相关的问题。

尽管尚未确定确切的根本原因、但我们在客户的实际电路中观察到了以下现象:

-

当 FET 导通时、偏置绕组电压上会立即出现较大的振铃。

-

这种振铃可能会导致 CS 电压检测错误、从而导致 DRV 信号在大约255ns 内关闭。

-

此行为始终在振荡停止之前立即观察到。

-

振铃将继续叠加、直到辅助绕组电压达到+20V、振铃频率约为12MHz、并大约需要1μs 稳定下来。

-

此时、我们怀疑这种振铃主要是变压器设计引起的。

根据上述情况、我们恳请您确认并回答以下问题:

问题1:

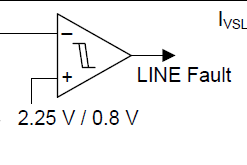

请阐明 I_VSL 数据锁存器的确切时序。

例如:在 DRV 信号开启后、CS 电压是否锁存为 A [ns]?

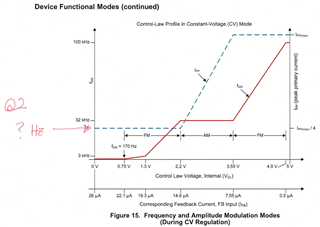

问题2:

在数据表的第16页(CV 模式运行)、请指明峰值电流 IPP 等于最大 IPP 的1/4时的开关频率(FSW)。

问题3

在应用手册 SLUAAC5中、发表以下声明:

图8-1中的 VAUX 振铃过大、在 TLK_RESET 期间振铃低于接地。

已知此行为可触发 UVLO 故障并关断转换器。

这是因为当 VS 引脚接地时、会激活输入 UVLO 故障。

这是否意味着、如果在 TLK_RESET 周期(当 DRV 关闭时)偏置绕组电压低于 GND、则可能立即触发错误的 UVLO 故障? 请确认。

问题4

关于 SLUAAC5中的公式(24)、所述的(max)是否可以解释为运行期间 CV 模式下的实际最大开关频率?

在客户电路中观察到的最大开关频率约为70kHz。

这种情况对时间敏感。 如果您不能立即获得完整的答复、我们非常感谢您提供您的答复的预计时间范围。

非常感谢您的友好支持与合作。

此致、

Conor