主题中讨论的其他器件: UCC21520

工具/软件:

您好、

我们想了解有关 UCC21551隔离式栅极驱动器的以下三个技术主题:

与 TI 的其他2通道增强型隔离栅极驱动器(例如 UCC21520)相比、UCC21551的价格显著降低。

我们假设这种成本差异可能是由于功能集、内部架构、隔离规格或制造工艺方面的差异造成的。

您能否说明有助于降低成本的主要技术或设计权衡?

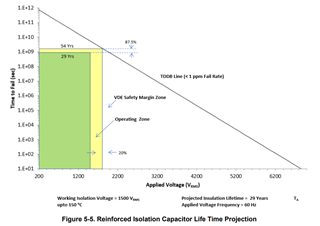

在商用交流线路相关噪声(例如50Hz 或60Hz 波形泄漏或交流纹波电压)持续耦合到隔离式栅极驱动器高侧端子的应用中、

是否担心由于内部隔离栅或输出级上的应力而导致的长期可靠性、降级或异常行为?

具体来说、如果此类低频交流噪声长时间跨隔离栅叠加、这是否会影响绝缘寿命或功能稳定性?

如果存在与此用例相关的任何内部评估或设计指南、如果您能分享这些详细信息、我们将不胜感激。

在半桥配置中、如果高侧和低侧 FET 同时意外导通(即击穿情况)、

隔离式栅极驱动器内预计会出现哪种失效模式?

我们尤其关注输出级的潜在损坏机制、内部电路击穿或此类应力下的绝缘故障。

在此条件下、如有任何已知的故障分析或测试结果、我们将不胜感激。

此致、

Conor