请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:UCD3138 工具/软件:

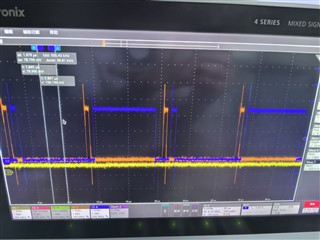

大家好。 我有一个问题,并真诚地希望你可以帮助我解决它。我配置了 DPWM1以下面的方式,操作它在正常模式。 我检查了 DPWMFILTERDUTIREAD 寄存器、该寄存器是一个常数值、因此波形应保持不变。 但是、出现了以下情况。

void init_dpwm1(void) // DPWM1B is used to drive 1st phase

{

Dpwm1Regs.DPWMCTRL0.bit.PWM_EN = 0; //disable everything

Dpwm1Regs.DPWMCTRL1.bit.GPIO_A_EN = 1; //turn off DPWM1A for now

Dpwm1Regs.DPWMCTRL1.bit.GPIO_B_EN = 1; //turn off DPWM1B for now

// Enable Current Limit and Set min duty cycle to verify.

Dpwm1Regs.DPWMCTRL0.bit.CBC_PWM_AB_EN = 1; // Enable cycle by cycle current limit.

Dpwm1Regs.DPWMCTRL0.bit.CBC_ADV_CNT_EN=1; //normal model 下配合CBC_PWM_AB_EN一起开启CBC

Dpwm1Regs.DPWMCTRL0.bit.BLANK_B_EN = 1; // Enable blanking so we can see a min pulse for curr lim,

Dpwm1Regs.DPWMCTRL0.bit.BLANK_A_EN = 1; // Enable blanking so we can see a min pulse for curr lim,避免误触发CBC电流

Dpwm1Regs.DPWMBLKBBEG.all = ((SWITCH_FREQ_NUMERATOR/switching_frequency) << 4)-1280;//消隐开始时间

Dpwm1Regs.DPWMBLKBEND.all = ((SWITCH_FREQ_NUMERATOR/switching_frequency) << 4);//消隐结束时间,给B通道配置了一个大约0.32us的消隐时间

Dpwm1Regs.DPWMBLKABEG.all = 0;//消隐开始时间

Dpwm1Regs.DPWMBLKAEND.all = 0x0500;//消隐结束时间,给A通道配置了一个大约0.32us的消隐时间

Dpwm1Regs.DPWMFLTCTRL.bit.B_MAX_COUNT = 2;//故障B计数,设置在断言故障之前在故障B输入上接收到的顺序故障数

Dpwm1Regs.DPWMFLTCTRL.bit.A_MAX_COUNT = 2;//故障A计数,设置在断言故障之前在故障A输入上接收到的顺序故障数

Dpwm1Regs.DPWMFLTCTRL.bit.ALL_FAULT_EN = 1; //enable this for OVP,允许故障保护

Dpwm1Regs.DPWMCTRL2.bit.SAMPLE_TRIG1_MODE = 1;//启用adaptive sample teigger B,实现平均电流模式采样

Dpwm1Regs.DPWMCTRL2.bit.SAMPLE_TRIG_1_EN = 1; //enable sample trigger1,开启1触发器,在前端EADC中应用

#if(PFC_TYPE == INTERLEAVED)//if this is interleaved PFC

Dpwm1Regs.DPWMCTRL0.bit.PWM_MODE = 3; //triangular mode

// Dpwm1Regs.DPWMCTRL2.bit.SAMPLE_TRIG1_OVERSAMPLE = 0; //NO oversampling.

Dpwm1Regs.DPWMCTRL1.bit.EVENT_UP_SEL = 0; //update right away

#elif(PFC_TYPE == BRIDGELESS)//if this is bridgeless PFC

Dpwm1Regs.DPWMCTRL0.bit.PWM_MODE = 3; //triangular mode

// Dpwm1Regs.DPWMCTRL2.bit.SAMPLE_TRIG1_OVERSAMPLE = 0; //NO oversampling.

Dpwm1Regs.DPWMCTRL1.bit.EVENT_UP_SEL = 0; //update right away

#else //single phase

#if ((UCD3138A==1)||(UCD3138064A==1)||(UCD3138A64A==1)||(UCD3138128A==1)||(UCD3138A64==1)||(UCD3138128==1))

Dpwm1Regs.DPWMEV1.all = 132*4; //aviod 132ns events update window

Dpwm1Regs.DPWMEV3.all = 132*4; //aviod 132ns events update window

#else //non A version

Dpwm1Regs.DPWMEV1.all = 2000;//周期开始后的500ns为A的上升沿,500ns的死区时间

Dpwm1Regs.DPWMEV2.all = 0;//500ns的死区时间

Dpwm1Regs.DPWMEV3.all = 2000;//DPWMEV3-DPWMEV2为AB的死区时间

Dpwm1Regs.DPWMEV4.all = ((SWITCH_FREQ_NUMERATOR/switching_frequency) << 4);//距离周期还有500ns时为B下降沿

#endif //((UCD3138A==1)||(UCD3138064A==1)||(UCD3138A64A==1)||(UCD3138128A==1))

Dpwm1Regs.DPWMCTRL0.bit.PWM_MODE = 0; //Normal Mode

// Dpwm1Regs.DPWMCTRL2.bit.SAMPLE_TRIG1_OVERSAMPLE = 3; //8X oversampling.

//Dpwm1Regs.DPWMCTRL1.bit.EVENT_UP_SEL = 0; //update right away

Dpwm1Regs.DPWMCTRL1.bit.EVENT_UP_SEL = 1; //update at end of period

#endif

Dpwm1Regs.DPWMCTRL0.bit.CLA_EN = 1;//闭环

Dpwm1Regs.DPWMCTRL0.bit.PWM_EN = 1; //enable OK here, because nothing will happen until DPWM and front end are globally enabled

}

两个正常循环之间会有一个异常循环。这是否与 CBC 有关? 因为它总是遵循一个正常周期、但有一个异常周期。

两个正常循环之间会有一个异常循环。这是否与 CBC 有关? 因为它总是遵循一个正常周期、但有一个异常周期。