工具/软件:

您好:

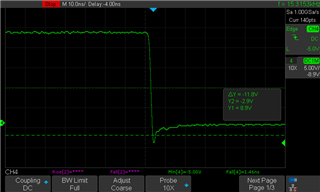

我目前使用直流/直流控制器实现24/5V 降压转换器。 我正在验证谴责、我观察了开关节点中的过冲情况、以确保不会超过最大绝对额定值。 数据表中开关节点引脚的额定值为-3V、在100ns 内为33V。 但在我的情况下,我来指责以下问题:

关断过冲达到-5V、 导通电压为-500mV 时为基础值、而导通电流不在图像中、但测得的电压约为500mV

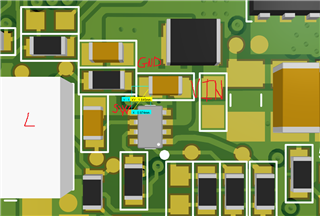

此测量是通过使用示波器 Teledyne T3DSO124 of 200MHz BW 和1GSa/s 来完成的、使用的探头是带200MHz CAT BW 的探头。 如 PCB 中所示、我测量以下点:

我正在最接近的去耦输入电容器中使用 GND 进行测量、而我直接在 SW 引脚中进行测量。 我想知道为什么关断过冲是完美的(大约500mV 过冲和24V 输入)、但导通过冲达到-5V。 此外、虽然 IC 已经远远超过了建议的运行条件、但我想知道您是否可以帮助我解决这个问题。 我想了解这种过冲的来源和设计中的操作、此外、我想知道是否应该很快排除 IC 之外。

此致、

David