工具/软件:

您好、

我计划 在5W 的反激式转换器中使用 UCC28704。 当我的变压器辅助绕组电压为14V 时、此 PSR 控制器能否在14V VDD 输入下工作、因为数据表说没有最大额定值、最大值为35V。 但我看到、UVLO Vdd (on)阈值的典型值为21V。 这对我来说是有效的吗?

提前感谢您的帮助。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

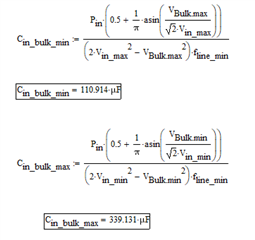

感谢您的答复。 对于大容量/输入电容器、我有另一个疑问。 我尝试使用 IC 数据表(第27页)中给出的相同公式来计算 CBULK 值、但我获得的值太高(约340uF)、但使用保持时间为5ms 的实际反激式 Cin 公式时、该值约为8uF。 我还检查了 TI UCC28704电子表格计算器中的值、大约为10 μ F。 我的怀疑是为什么使用数据表中的公式时它显示的值很大。 或者在哪种情况下、我们应该使用数据表中的 Cbulk 公式?

如果加以澄清、将会非常有帮助。 谢谢。

我的 Vin= 85V~265V VAC、Fline_min=48Hz、这是使用数据表中相同公式时得到的结果。

您好、Kavitha、

Ning Tan 本周不在办公室。

我以为我能忍住的,可是我完全错了。

下面的公式是用于确定 Cbulk (Cin_bulk_max)的正确公式。

我想真正的问题是:您为 VBULK.min 和 Vin_min 使用了什么值?

如果 I Use 引脚=5W、Vin_MIN = 85VAC、VBULK.MIN = 70V、则 CBULK = 8.1uF。

为容差增加20%、CBULK = 10.1uF。

实际上、如果 Pout = 5W、则引脚必须更高、因此 CBULK 将更高一些、但这不是问题所在。 重点是公式是有效的、因此一个或多个输入不正确。 我怀疑 Vbulk.min 设置得过高、这将导致电容非常大。

70Vdc 是 Vbulk.min 的典型值、适用于反激式、最小输入为85Vrms。

Hihger 或更低的 Vbulk.min 会影响 Cbulk、但也会影响匝数比。

请谨慎选择。

此致、

Ulrich

非常感谢您对 Ulrich Goetzke 的澄清