工具/软件:

尊敬的先生:

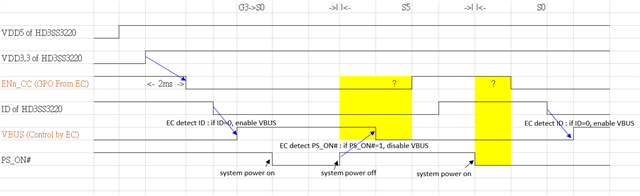

我们有一种主板设计、将 HD3SS3220用于 USB Type-C 端口、原理图如下:

为了省电、系统会在 OS 进入 SHUTDOWN 模式后禁用 VBUS 电源。

但是、我们遇到了一个问题、即 USB3功能在系统再次上电后变得不可用。

USB3故障似乎与重新施加 VBUS 后缺少 CC 重新协商有关。

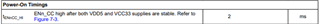

我们进行了一个实验、其中重新启用 ENn_CC (引脚29)信号解决了 USB3问题。 因此、我们考虑使用 GPIO 来控制 ENn_CC。

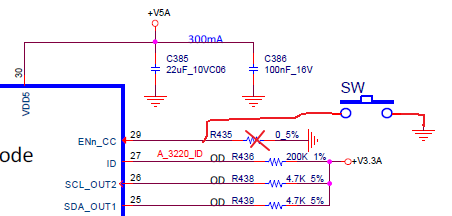

但是、数据表未提供 ENn_CC 控制的详细时序要求或行为。 我们担心不正确的 ENn_CC 控制可能会引入副作用。

您能否提供通过 EC 控制 ENn_CC 的时序指南或建议、以确保正确重新启用而不会导致问题?

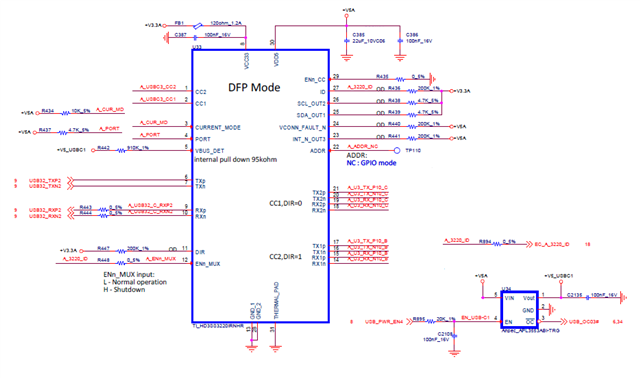

以下是使用按钮连接的引脚29和 GND 进行的重新启用实验的操作:

步骤1:当系统关断时、EC 将禁用负载开关、并且 VBUS = 0V

此时未按下该按钮、因此 ENn_CC 悬空。

步骤2:当系统上电时、按下按钮并将 ENn_CC 拉至低电平。

这将启用 ENn_CC、引脚27 (ID)被拉至低电平。

EC 检测到 ID = 0并打开负载开关、将 VBUS 恢复到5V