Thread 中讨论的其他器件: SN74HCT245

工具/软件:

我们将 在 TLC59283 之间使用一个缓冲器、并在两个 TLC59283 之间的输出引脚上接收到一个额外的位。

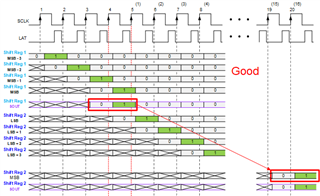

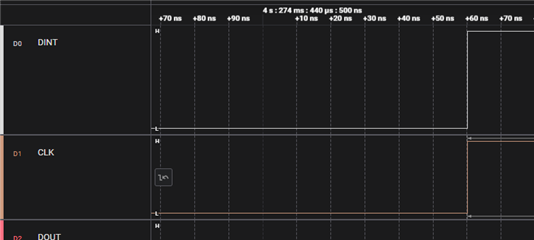

我在下面创建了几个图示、以展示我们看到的问题。

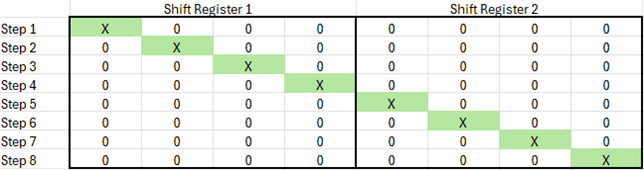

在每一步、我们都会向外推出一个额外的位、然后锁存

例如

推 1 位、锁存

按下 01 位、锁存

按下 001 位、闩锁

PUSH 0001 位、LATCH

这是正常的预期行为、以 8 个步骤显示(在我们的示例中,每个移位寄存器仅具有 4 位)

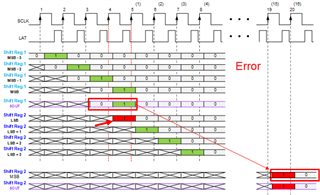

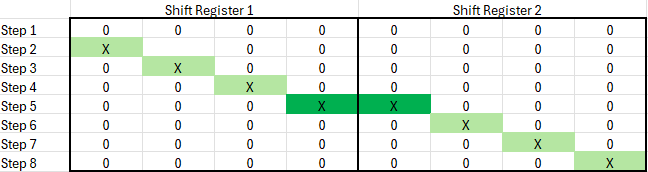

这就是我们将 74HCT245PW 放置在 TLC59283 移位寄存器之间时看到的结果。 还有一个额外的位移出。 在步骤 5 中、锁存时、两个寄存器上都可以看到一个位

在上面的步骤 5 中、我们按下了;0001 锁存

在步骤 6 中、我们按下 00001 锁存器 、但由于步骤 5 中的额外位、该位有额外的一个步长。 在每个步骤之后都会发生。 如果我们将更多 TLC59283 与中间的缓冲器连接在一起、就会在每个移位寄存器之间不断增加一个额外的位。

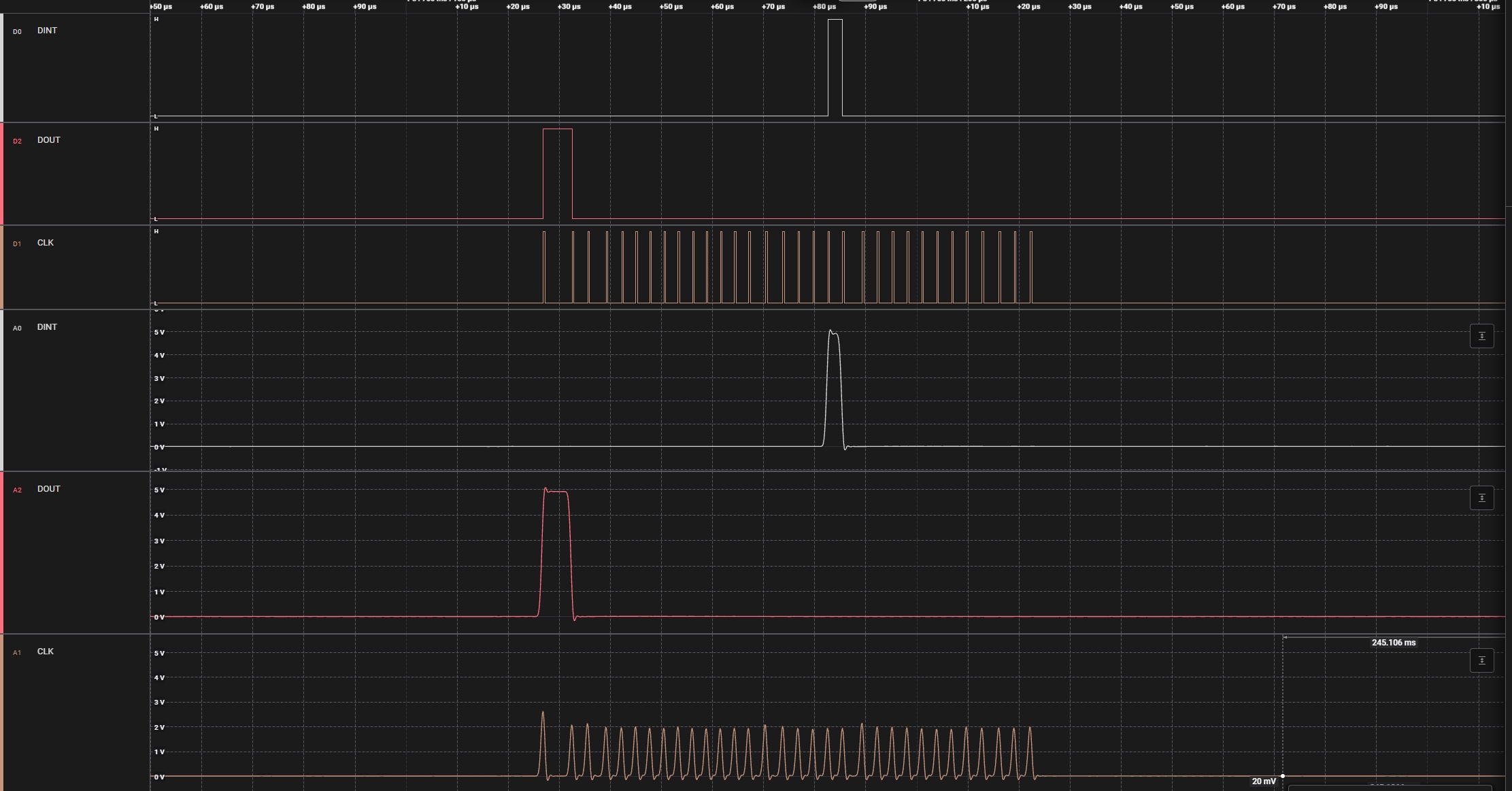

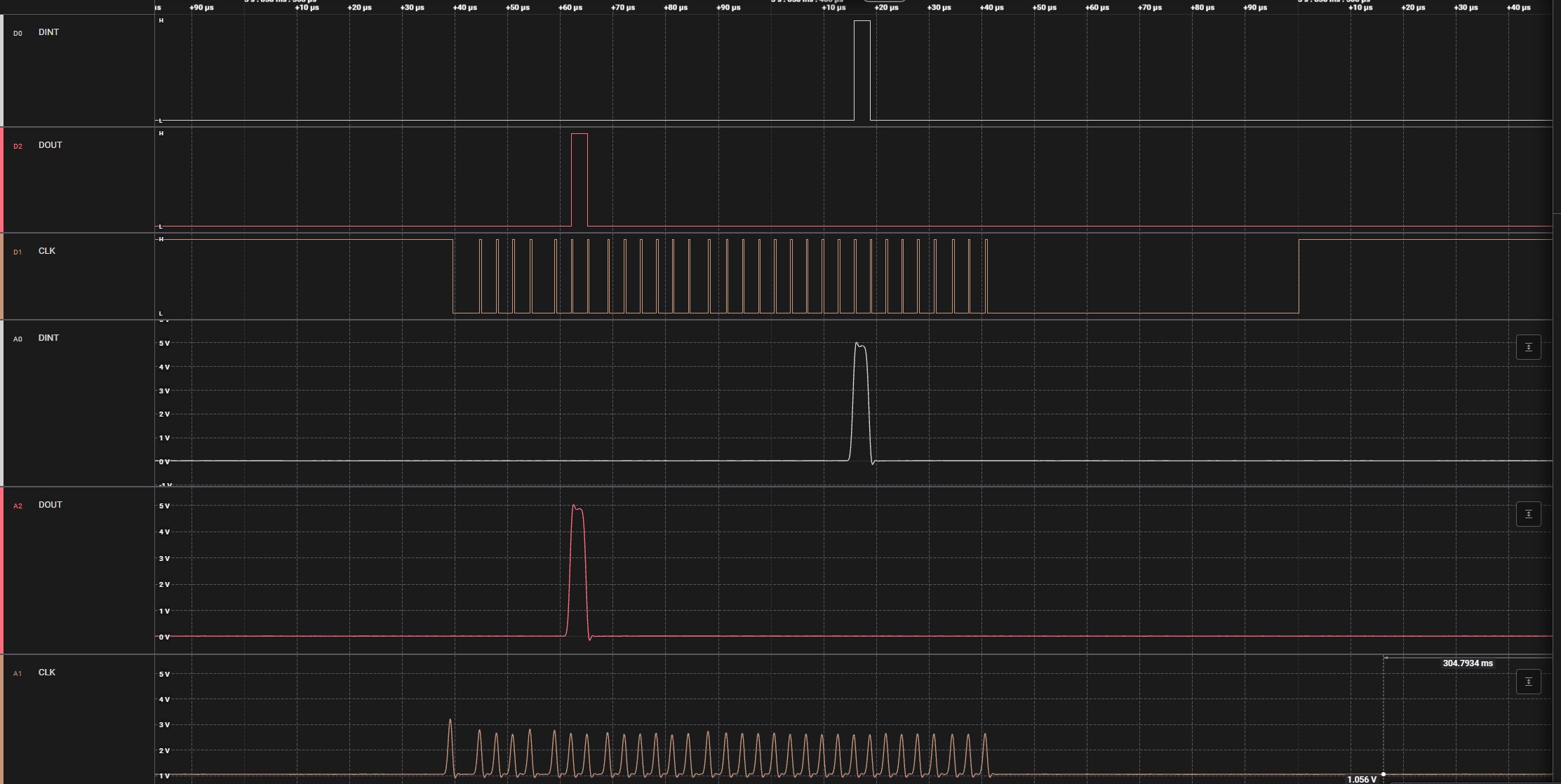

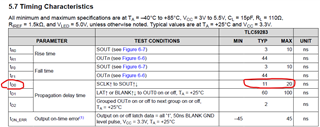

我们已经将其缩小到时钟引脚。 如果我们从缓冲器中移除时钟并直接连接 TLC59283 ,问题就会消失。

如果我们手动调整引脚(以消除 MCU 的任何速度问题)、也可以重新出现此问题。

我们想使用缓冲器、因为要将多达+30 个移位寄存器链在一起

有人可以提供任何建议吗?

提前感谢!