工具/软件:

您好:

我有一个使用可拆卸电源的设计。 在不向系统发出警告的情况下、可以随时移除电源。 我想知道该具有 SPLYGD 引脚的器件是否可用于自动禁用下游电源以支持特定的断电序列。 当系统中的各种大容量电容放电时、这主要是一个竞态条件、因此我主要对此 IC 的时序规格感兴趣。

我的问题是:

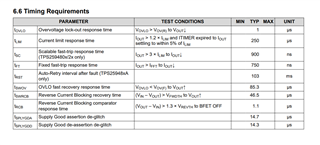

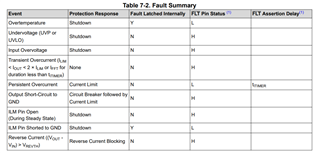

1) 移除 VIN 后、电压将根据输入端的大容量电容而下降。 是否有从电压降至 UVLO 阈值以下且 SPLYGD 引脚拉至低电平开始的持续时间规格?

2) 该器件的最小输入电压范围为 3.5V。 如果我的 UVLO 设置为 4V、SPLYGD 引脚行为是否可以可靠、直到 VIN 降至 3.5V 以下? 当电压低于 3.5V 时会发生什么情况?

3) 是否最好改用 FAULT_N 引脚来实现此目的? 下降至 UVLO 阈值以下是否会有更短的响应时间?

谢谢、

Ryan