工具/软件:

您好~

我有几个问题。

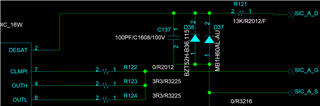

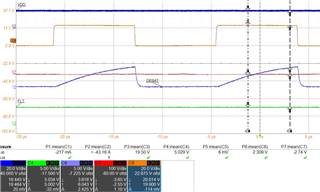

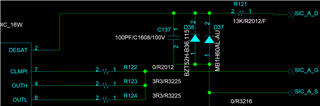

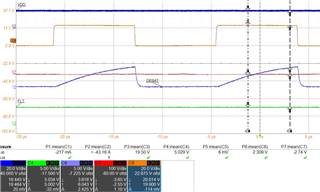

1.当我设计并测量 DESAT 电路时(如下所示)、它的工作原理如测得的波形所示。 请检查它是否正常工作。

2.如果去饱和设置值为 7.52V、那么去饱和是如何工作的? 如果它大于 9V 的固定值、去饱和是否起作用、如果它变小、去饱和是否起作用?

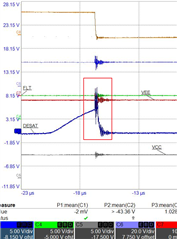

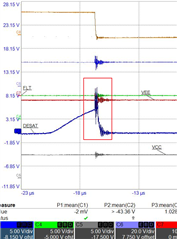

3. 当 Gate 打开和关闭时, Deset 波形中会出现峰值噪声。 为什么会发生这种情况?

4.去饱和电路的 CBLK 值的范围是多少?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好~

我有几个问题。

1.当我设计并测量 DESAT 电路时(如下所示)、它的工作原理如测得的波形所示。 请检查它是否正常工作。

2.如果去饱和设置值为 7.52V、那么去饱和是如何工作的? 如果它大于 9V 的固定值、去饱和是否起作用、如果它变小、去饱和是否起作用?

3. 当 Gate 打开和关闭时, Deset 波形中会出现峰值噪声。 为什么会发生这种情况?

4.去饱和电路的 CBLK 值的范围是多少?

嗨、Junehee、

1.看起来您的 DESAT 引脚在每次 OUT 变为高电平时都会充电至固定值、这是正常运行情况下的预期结果。 在去饱和事件中、DESAT 引脚电压将一直充电至 9V、然后输出将关闭、即使输入仍然为高电平也是如此。 然后、nFLT 将拉至低电平并锁存。

2. Vdesat_actual 意味着当 VCE 达到 7.5 时、由于去饱和二极管压降和串联电阻压降、DESAT 引脚上的电压将充电至 9V 阈值。 因此、该电路有效地检测 VCE 是否高于 7.5V(而不是 9V)。

3.当输出切换时、通常会有噪声注入 DESAT 电容器。 这仅仅是由于寄生耦合和引脚的接近。 最重要的是抑制 OUT 上升沿上的此噪声注入、因为这可能会破坏 DESAT 时序。 因此、有一个前沿消隐时间、噪声在该时间内通过闭合开关 (t_DESAT LEB) 进行分流。 由于输出已经关闭、因此不应在下降沿触发 DESAT。

4.电容可以根据需要尽可能大、但如果 DESAT 触发速度不够快、IGBT 会受损。 另一方面、通常可以使用低至 50pF 的电容器。 但低于该值会产生抗噪问题。 也就是说、噪声注入开始改变 DESAT 电压。 在不减小该电容值的情况下缩短 DESAT 时间的一种方法是在 VDD 与 DESAT 之间使用外部电阻器。 这会增加充电电流、并允许使用容噪性能更高的较大电容器。

此致、

Sean

嗨、Junehee、

DESAT 电流默认为 500uA。 如果您希望将电容器尺寸加倍并保持相同的 DESAT 触发延迟、则需要再添加 500uA。 如果 VDD 的电压为 15V、则可以使用的电阻是 15V/COM 0.5mA = 30k Ω。

除了将噪声集成到更大的电容器之外、您实际上无法消除外部的噪声注入、但前沿消隐时间是设计用于在内部分流噪声。 噪声在下降沿不应该很重要、因为 DESAT 已在下降沿停用。

此致、

Sean