主题中讨论的其他器件:LM7480

工具/软件:

大家好

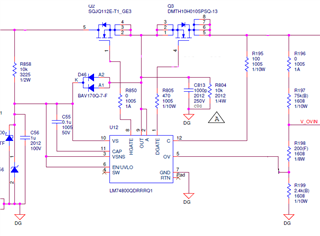

我们使用 LM7480 来防止过压、过流和负载突降、并确认其正常工作。

后续电路的设计注意事项

我们发现了测量波形的一个问题。

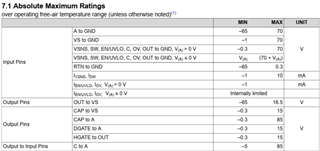

器件在 DGATE 和 A 端子之间的绝对最大额定值指定为–0.3V 至 15V、如下所示。

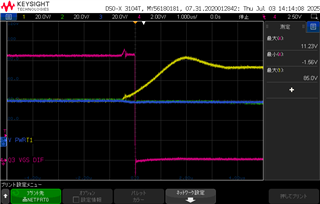

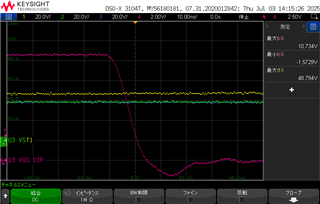

我们根据 JASO D001 标准(类似于 ISO 16750-2 和 ISO 7637-2 标准)测试的波形如下所示。

DGATE 和 A 端子之间在电压低于–0.3V 时有大约 10ns 的下冲

CH1:黄色:电源输入

CH2:绿色:Q3 FET 源极(A 引脚)Ω

CH3:蓝色:Q3 漏极

CH4:Red:Q3 Vgs

从上至下的右侧窗口:VGS 最大值、VGS 最小值、电源输入最大值。

由于这是使用高压差分探头进行测量的、因此探头的电容或电感可能会影响测量结果。

1.这种现象可能对设备产生哪些负面影响?

2.这个问题有哪些可能的解决办法?