Thread 中讨论的其他器件: UCC27212

工具/软件:

您好:

我的直流/直流转换器出现故障、导致高侧 MOSFET 比高电平信号更早关断。

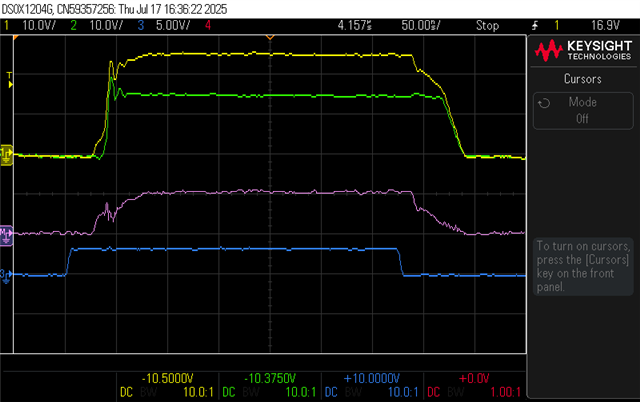

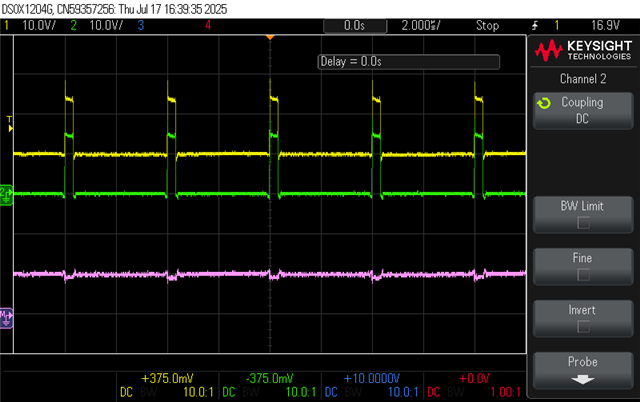

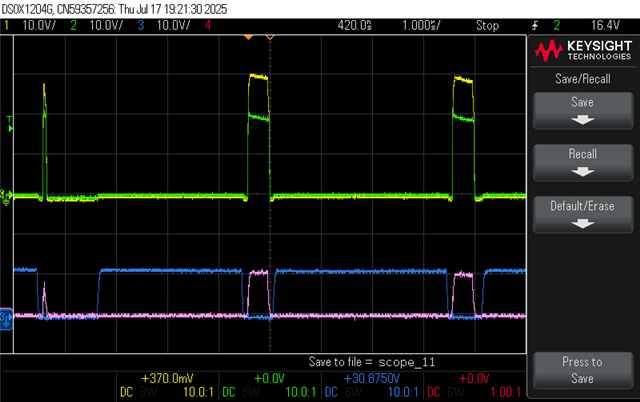

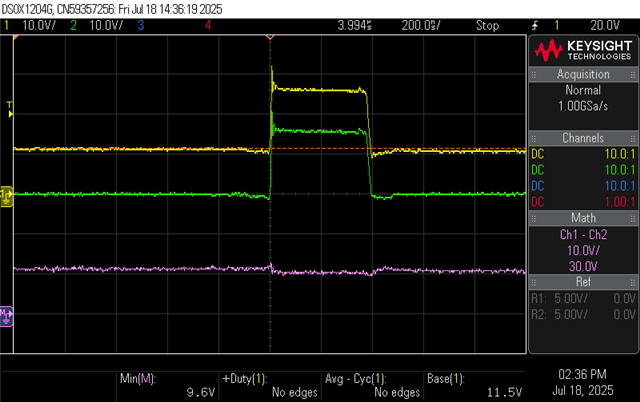

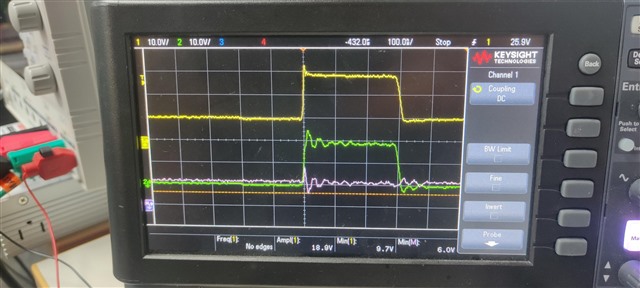

正常脉冲 (200ns)

- CH1 = HS - GND

- Ch2 = HO - GND

- 紫色= HO-HS

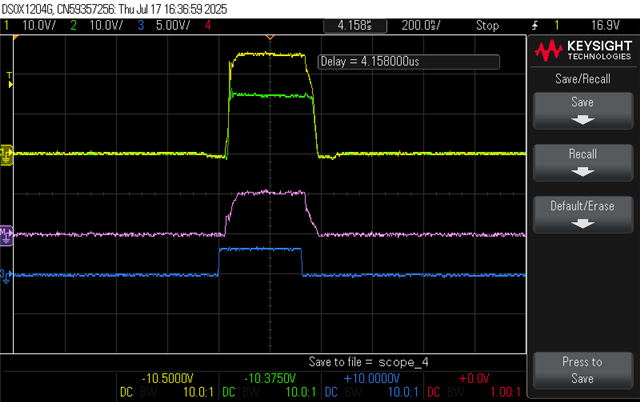

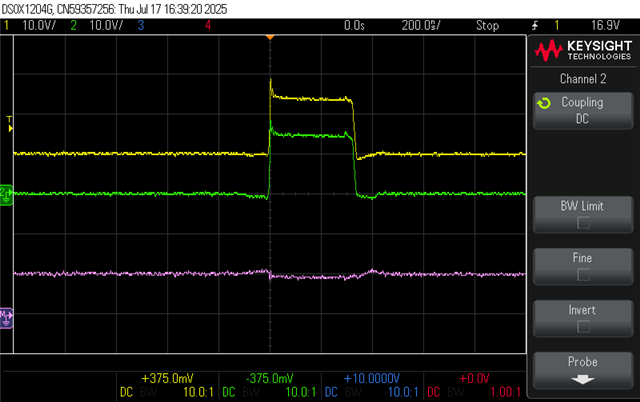

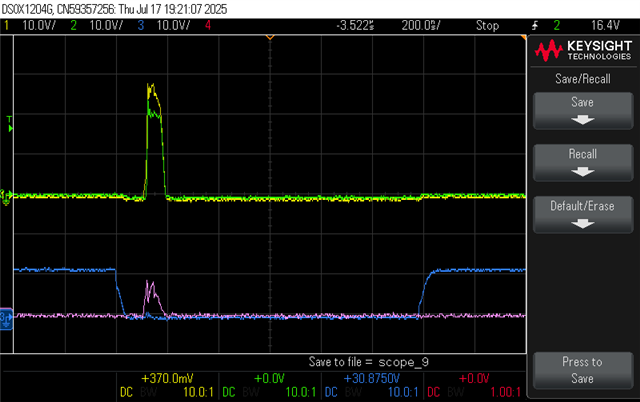

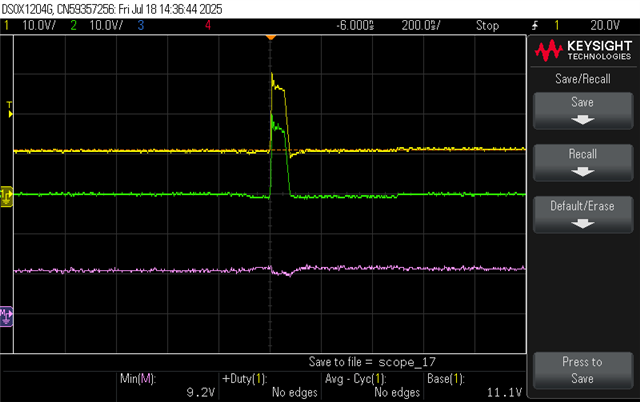

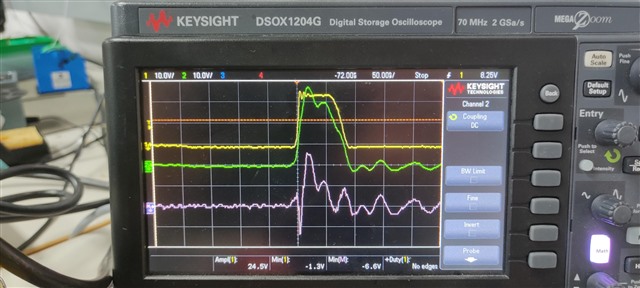

异常行为 (70ns)

- CH1 = HS - GND

- Ch2 = HO - GND

- 紫色= HO-HS

现在、我怀疑有 2 种不同的可能性:

-栅极驱动器的 UVLO 关闭了 HO

- HO 栅极振荡变得足够低,以关闭 MOSFET ,它不会在之后再次打开(因为自举电容器放电?)

我测试过的内容:

- HI 和 LI 似乎很稳定、我根据栅极驱动器附近的 GND 测量了 HI 和 LI。 虽然 HI 和 LI 上的脉冲长度保持稳定、但 HO 上的脉冲偶尔会更短。

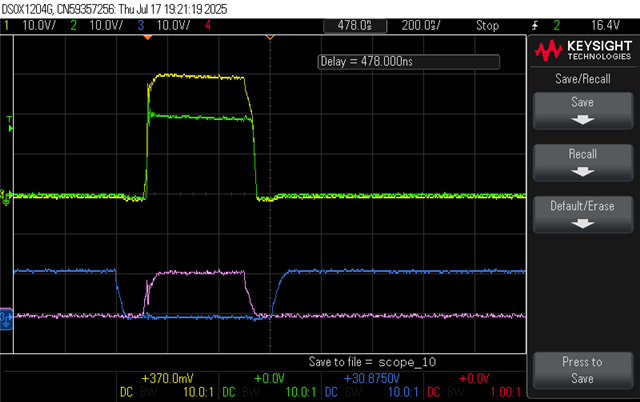

- 自举电容器 :我使用的是一个 100nF 电容器,我直接焊接在引脚 HB 和 HS。 之前、我在 PCB 的底部并联了一个 100nF 和 1uF 电容器、然后通过过孔连接到 HB 和 HS 引脚

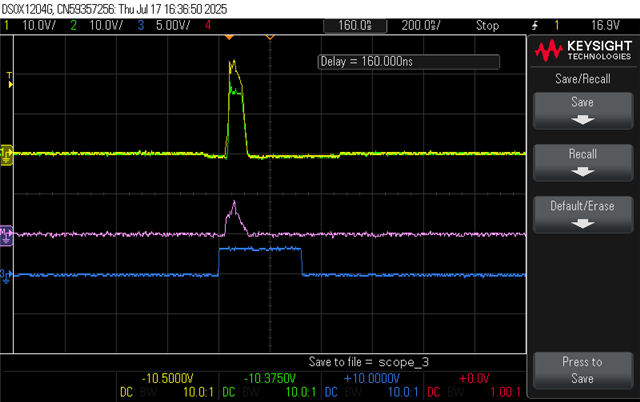

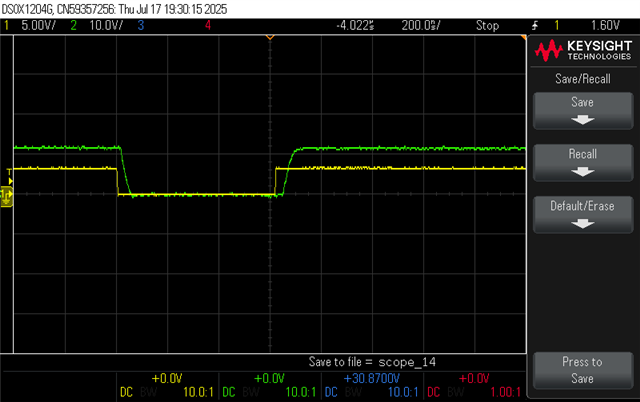

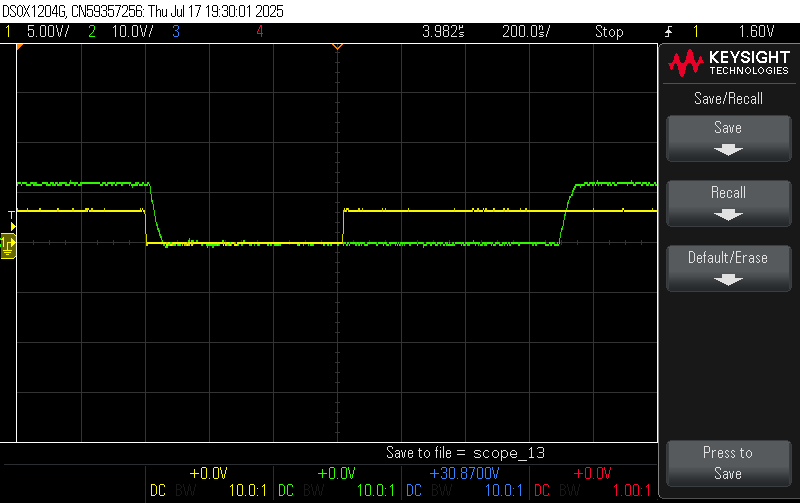

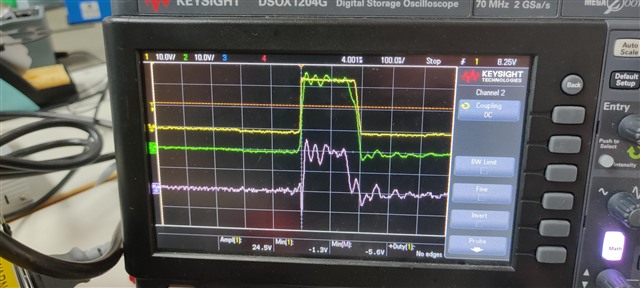

我测量了自举电容器上的电压。 它似乎下降至低于 UVLO 阈值、但我不确定 UVLO 是否会在这个短时间内激活。 其他地方、我读到 UVLO 的延迟为 1us。

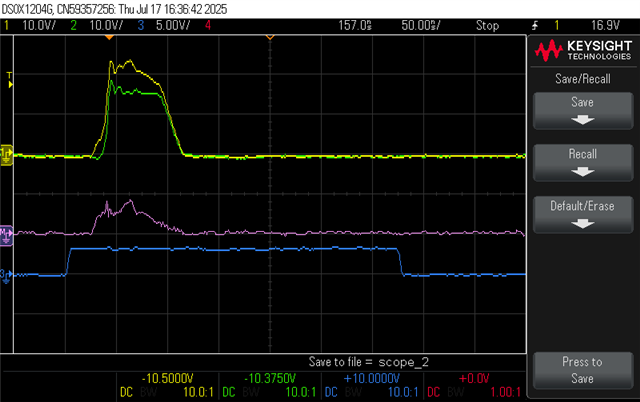

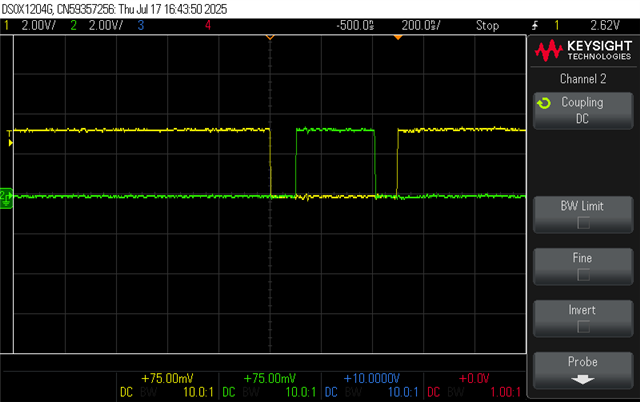

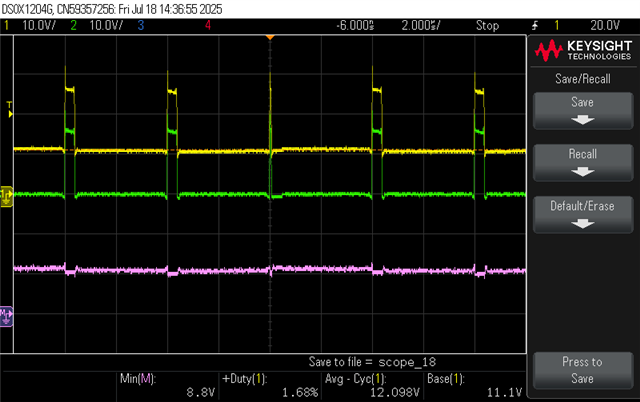

自举电容器

- CH1 = HS - GND

- CH2 = HB - GND

- 紫色= HB-HS

- VCC :我测量了 VCC 电容器上的电压。 我使用一个 1uF 电容器。 VCC 引脚上的电压似乎保持稳定

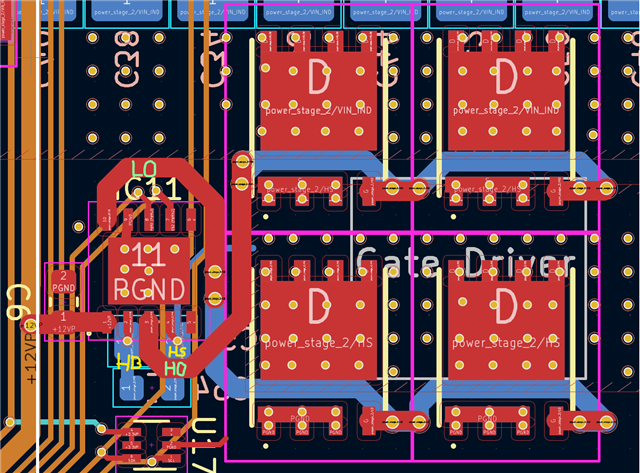

-栅极电阻 :我尝试了不同的栅极电阻器。 高于 5 欧姆的栅极电阻似乎可以改善该行为。 由此我得出结论、异常行为是由 HS 栅极上的振荡引起的。 HO 和 LO 的布线相当长、会导致高电感。

e2e.ti.com/.../board_2D00_power_5F00_stage_5F00_2.pdf

e2e.ti.com/.../board_2D00_power_5F00_stage_5F00_2.pdf

在下一次设计迭代中、我计划尽可能缩短 HO 和 LO 布线。 此外、自举电容器将放置在栅极驱动器旁边的上侧、并降低至 100nF。

但我仍在尝试找出这个问题的根本原因。 该行为是否会由 UVLO 引起? 或者是栅极的振荡是导致 MOSFET 关断的原因。

非常感谢您的帮助

此致

Lars Pfueller