Other Parts Discussed in Thread: TPS628303, TPS54318, TPS628503, TPS628513

主题中讨论的其他器件: TPS628503、TPS628303、 TPS628513

工具/软件:

尊敬的 TI 论坛:

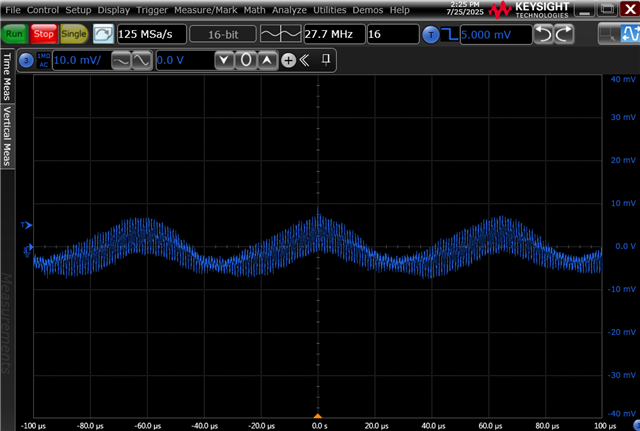

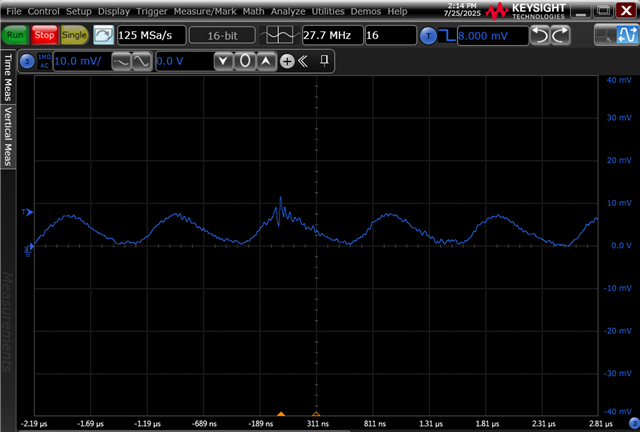

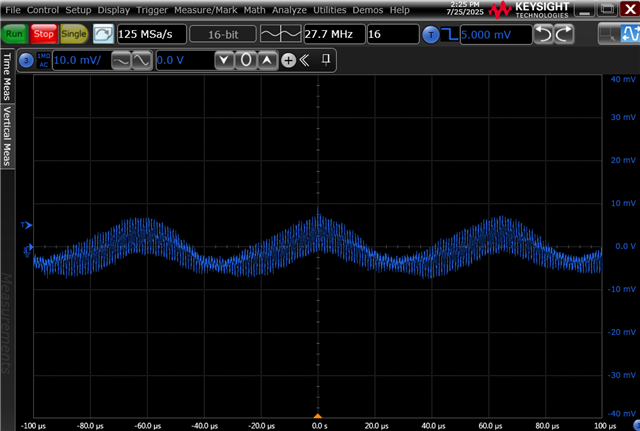

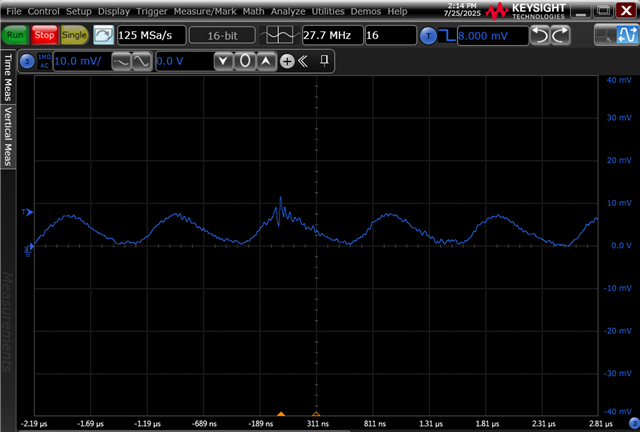

我已经测量了 TPS54318 的输出电压纹波。 除了大约 8mV_pp 的开关噪声之外、还有一个大约 12kHz 的拍频、这会将总输出电压偏差增加到 16mV_pp

这是由内部电压调节造成的?

谢谢你。

此致

Moritz

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: TPS628303, TPS54318, TPS628503, TPS628513

工具/软件:

尊敬的 TI 论坛:

我已经测量了 TPS54318 的输出电压纹波。 除了大约 8mV_pp 的开关噪声之外、还有一个大约 12kHz 的拍频、这会将总输出电压偏差增加到 16mV_pp

这是由内部电压调节造成的?

谢谢你。

此致

Moritz

尊敬的 Varun:

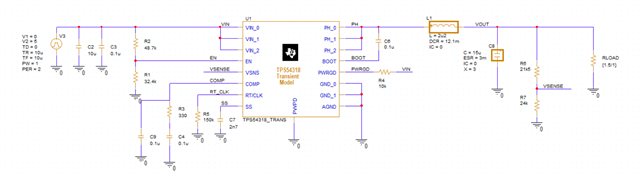

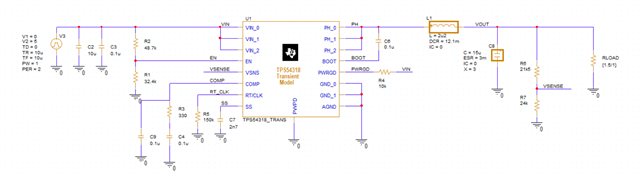

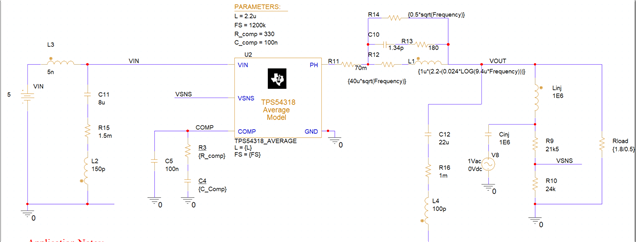

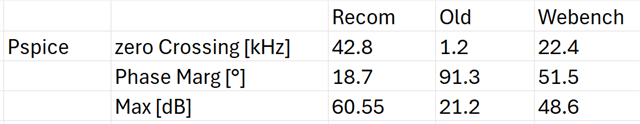

感谢您对补偿网络的想法。 它来自现有的设计、似乎并不理想。 我在 Webench 中快速检查了它、当时没有抛出任何错误。 我无法在 PSpice 中将它们一起绘制:

原理图如下:

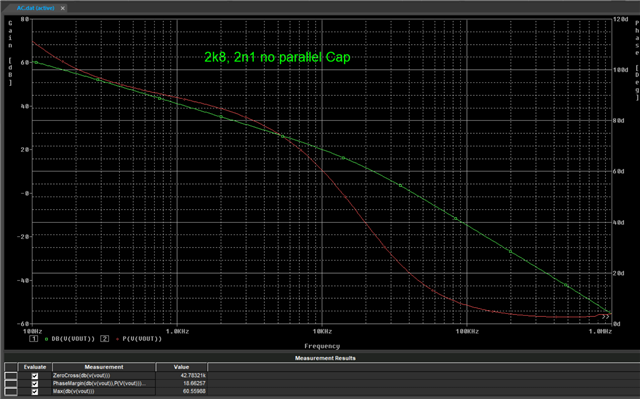

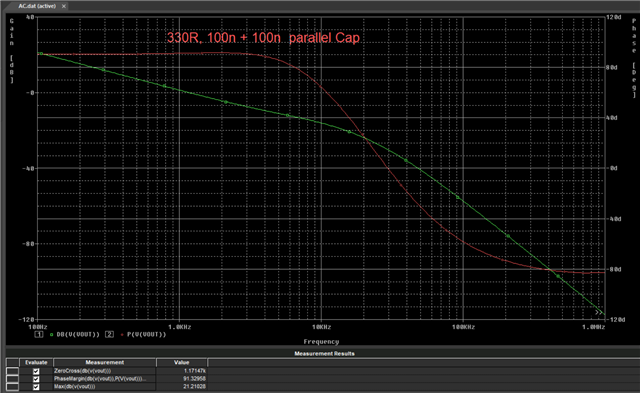

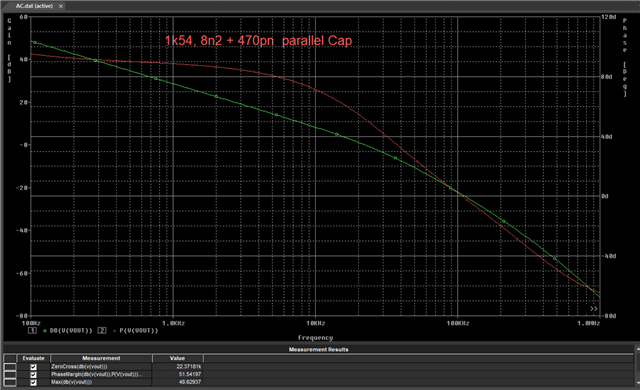

这是您的建议 (ZeroCross (db (v (Vout))) 42.78321k PhaseMargin (db (v (Vout))、P (V (Vout) ))–180 18.66257 Max (db (v (Vout)) 60.55988)

与当前设计的关系:(ZeroCross (db (v (Vout))) 1.17147k PhaseMargin (db (v (Vout)))、P (V (Vout)))–180 91.32958 Max (db (v (Vout)) 21.21028)

vs. webench 工具

有限过零 BW 可能会成为这里的问题吗?

几天后、我将使用修改后的设计进行一些测量。

此致

Moritz

尊敬的 Moritz:

感谢您运行仿真并进行总结。 我发现我推荐的 C4 值太低。 该值需要像 Webench 建议的值一样更高、以便 R3 和 C4 的零点以较低的频率出现并提供相位提升。

借助电路板上的电流补偿、交叉点非常低。 但是、相位裕度看起来很好。 由于带宽低、器件的 PSRR 在较高频率下很低。 您是否还能在输入电源上检查在 12kHz 下是否有任何噪声? 如果是、则可能会在没有太多衰减的情况下传递到输出。

此致、

Varun

尊敬的 Varun:

感谢您的更新。 关于 PSpice 模块:

有没有任何原因模型这么慢. 与 Wilmington 的公司相比,这是真的很难与他们合作。 更不用说扫过任何东西了。

PSpice for TI 刚刚停止工作了 两天、这毫无帮助。 (e2e.ti.com/.../5956366)

下周我将修改 PCB 并分享测量结果。

此致

Moritz

尊敬的 Varun:

我将补偿调整为 C4 = 10nF、R3 = 3.3k。 C5 = NC。

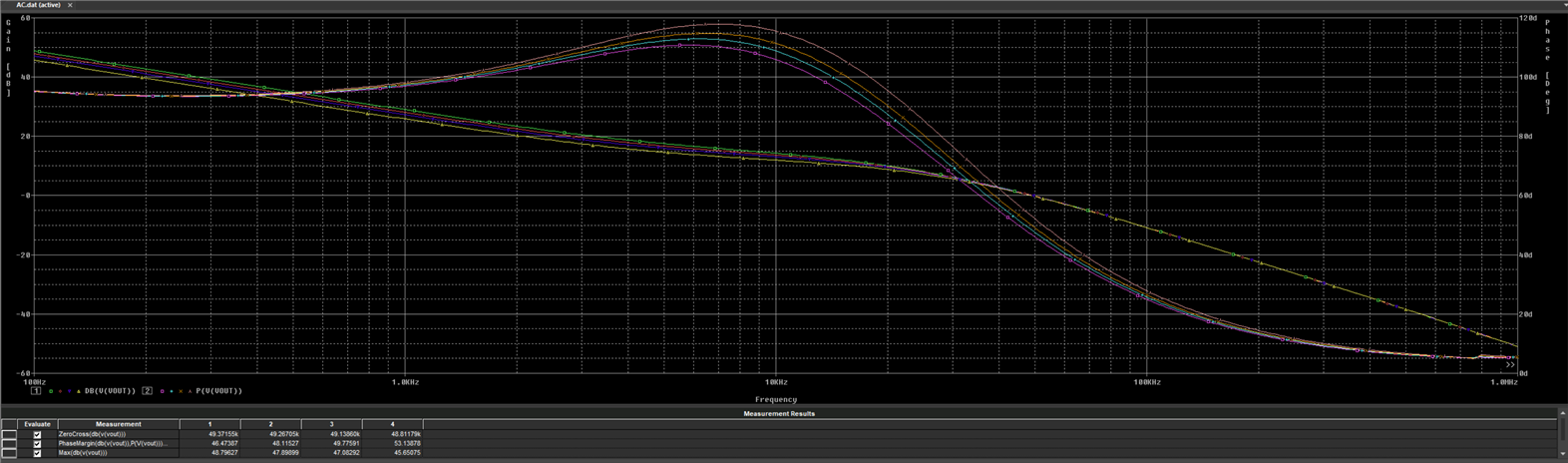

根据中的 PSpice 结果:

I OUT 1mA 250mA 500mA 1A

1 零交叉 (db (v (Vout))) 49.37155k 49.26705k 49.13860k 48.81179k

1 PhaseMargin (db (v (Vout))、P (V (Vout)))–180 46.47387 48.11527 49.77591 53.13878

1 最大值 (db (v (Vout))) 48.79627 47.89899 47.08292 45.65075

我尝试最大化 BW、以减少过冲。

拍频也降至 10mV(16mV 之前)、表明通过增大环路 BW 来增大 PSRR。