工具/软件:

我使用 TPS4811 进行设计。 然后、我想知道 INP 引脚的内部下拉电阻值。 我设计将 3.3k Ω 作为上拉电阻器。 在这种情况下、当信号开路时、该 IC 是否由该上拉电阻器驱动?

此致、

Nakagawa

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

我使用 TPS4811 进行设计。 然后、我想知道 INP 引脚的内部下拉电阻值。 我设计将 3.3k Ω 作为上拉电阻器。 在这种情况下、当信号开路时、该 IC 是否由该上拉电阻器驱动?

此致、

Nakagawa

你好、Rishika、

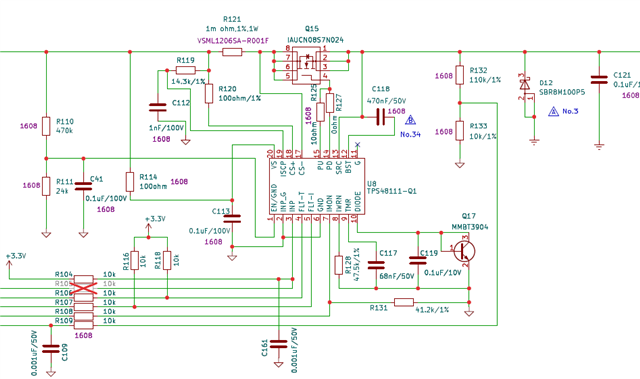

感谢您的合作。 遗憾的是、我无法将电路图采用此格式、但我的设计在 INP 上放置了 10k 电阻器作为上拉电阻器。 所以、我的图片是驱动外部 FET、栅极驱动、即使输入信号未连接到 INP 上也是如此。 然而,这个 IC 没有驱动,我不理解的原因。

我有两个错误设计、

1) 一种是在 10 引脚处使用 0.1uF、在“二极管“处使用旁路电容器、在本评估板电路图中使用 1000pF。

2) 接下来、P36 在此数据表中、图 9-18、CSCP 在 ISCP/CS-处放置 1nF。 我漏掉了、在 ISCP/GND 处放置 1nF。

我不知道为什么这些不起作用。 请告知我上述错误是否有理由不驾驶。

此致、

Nakagawa