工具/软件:

您好、

请您澄清一下 UCC28950 的软启动行为。

【背景】

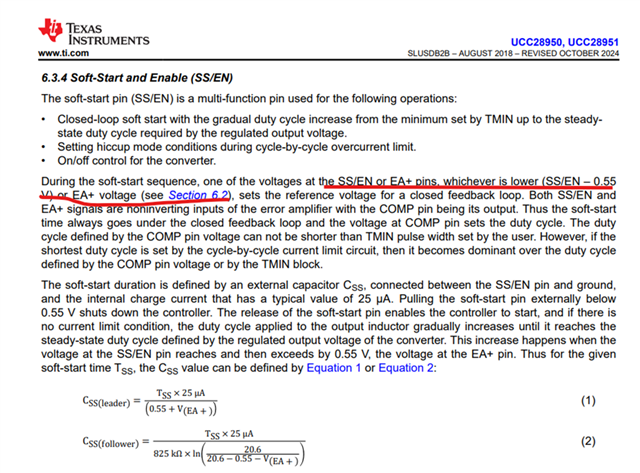

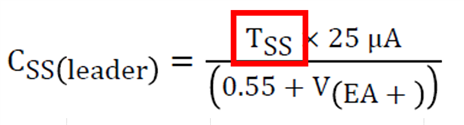

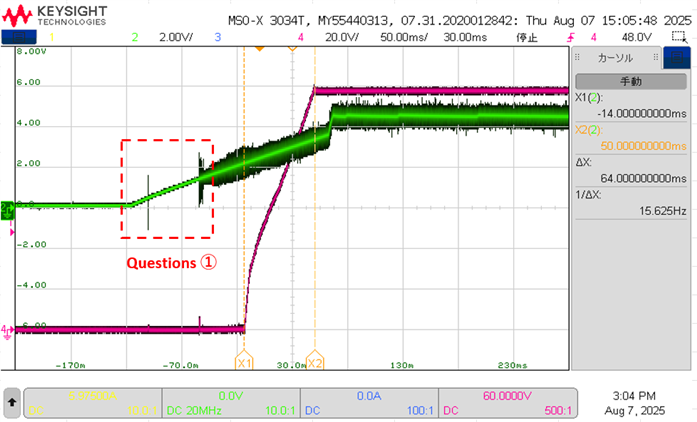

根据数据表中的公式 (1)、软启动时间 TSS 的计算公式如下:

当 CSS=Css 1 µF、EA+=2.5V、25µA 时、计算结果为:

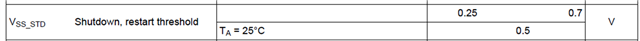

| 参数 | 数据值 | 注释 |

|---|---|---|

| CSS | 1 µF | |

| EA+ | 2.5V | 假设使用 Vref 分频器 |

| ISS | 25µA | 典型值 |

| Tss | 122ms | 已计算 |

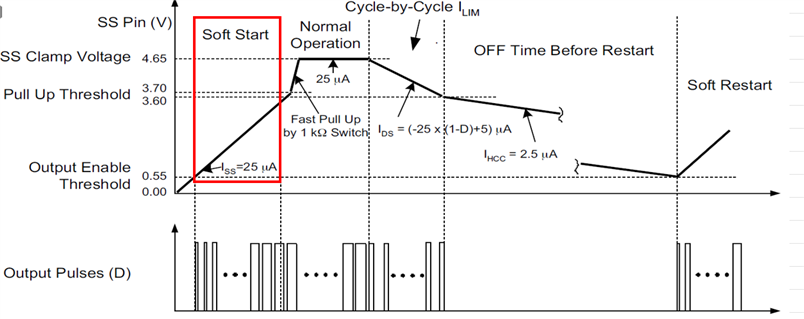

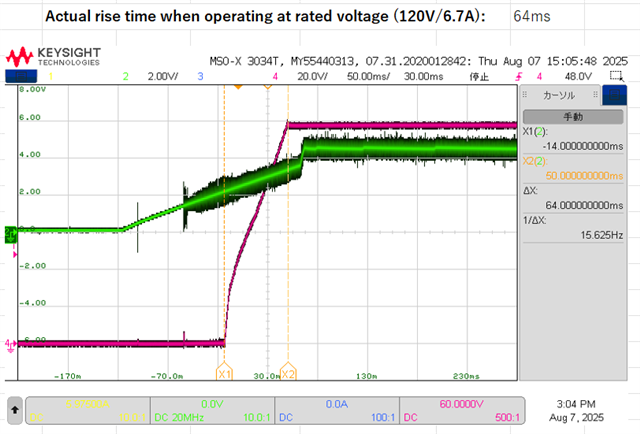

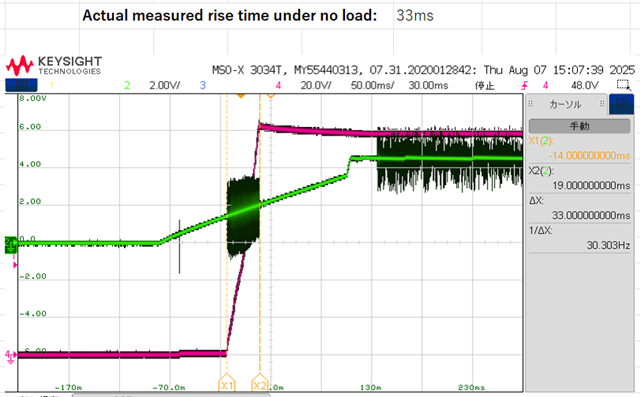

然而、实际测量结果显示上升时间较短:

-

额定负载 (120V/6.7A) 时:输出上升≈64ms

-

空载时:输出上升≈33ms

两者都明显短于计算出的 Tss (122ms)。

【问题】

在图 6-15 中、软启动≥从 VSS ① 0.55V 开始。但是、在测量中、输出仅在 VSS 超过约 1V 后才开始上升

-

由于 VSS 的额定电压高达 0.7V(最大值)、您能否阐明为什么会出现这种差异?

-

我们在 0.5V 左右观察到一些类似噪声的行为、但实际启动发生在 VSS 超过~1V 后

Δ t TSS ② 为占空比逐渐增加的周期。

-

IC 规格定义了最大占空比(典型值为 95%)是否正确?

-

在我们的测量中、即使在额定负载下、占空比也会在 50%左右饱和。 这是预期行为吗?

③ 测得的输出上升时间短于计算得出的 TSS、通常约为一半。

-

我们的理解是、当 VSS 达到 EA+时、即确定有效上升时间、此时输出电压稳定到其目标、具体取决于负载所需的占空比。

-

您能否确认 TSS 是否正确解读为占空比从 0%增加到 95%(典型值)的时间、而实际输出上升时间取决于负载条件和输出电压达到调节值的占空比?

TSS=100ms 的示例:

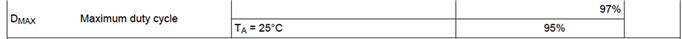

| 加载条件 | 已达到占空比 | 上升时间(计算值) |

|---|---|---|

| 空载 | 10% | 10.5ms |

| 额定负载 | 50% | 52.6ms |

| 重负载 | 70% | 73.7ms |

因此、输出上升时间随负载条件而变化、并不总是与计算得出的 TSS 匹配。 您能否确认这一理解?

我们感谢您对这些问题的反馈。

此致、

Conor