工具/软件:

我已经确定 P 沟道 FemtoFET CSD25501F3 适合成本敏感型应用、在偏置关断时需要低漏源漏电流。

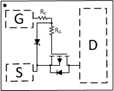

我的问题是、我是否可以依靠最大 如果栅极正向偏置、从而导致栅源两端出现标称结二极管压降、则持续的漏源漏电流规格 (50nA)? 将有一个额外的 100k 外部电阻器施加到栅极以更好地对 FET Cgs 进行去耦、因此与 RC 串联、进一步限制了高达 9V 正偏置下的内部正向保护二极管电流、但我目前不确定产生/反向场电压(结二极管的 Vf) 对)对引用的漏源漏电流可能产生的影响。