请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

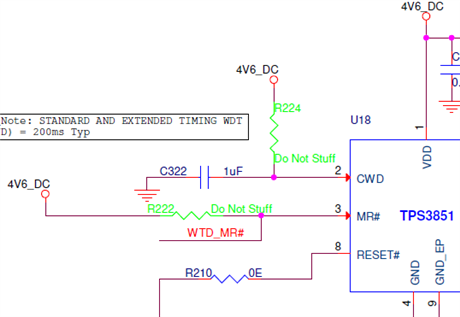

器件型号:TPS3851工具/软件:

您好的团队、

对于看门狗 IC 的 MR#引脚、我们有一个疑问。

我们设计了 IC、如上所述。

我们的意见如下

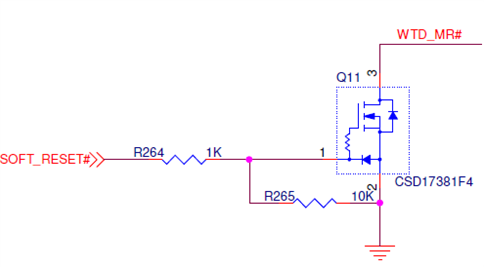

1.我们在 SOFT_RESET#引脚上输出 1.8V 逻辑高电平、然后 WTD_MR#引脚将 0V 显示为逻辑低电平。

2.我们在 SOFT_RESET#引脚上使逻辑低电平为 0V、然后 WTD_MR#引脚变为 1.1V 逻辑高电平。 由于 MR#引脚有一个内部上拉电阻、这是一个意想不到的 MR#引脚值。

3.之后、我们移除 Q11、此时 WTD_MR#引脚也显示 1.1V 逻辑高电平。

4.当我们在 R222 上安装 10k 上拉电阻时、WTD_MR#引脚仅显示 4.6V 逻辑高电平值。

为什么这个 MR#引脚显示这个 1.1V 逻辑高电平状态? 请说明这种奇怪行为背后的原因。