工具/软件:

您好专家、

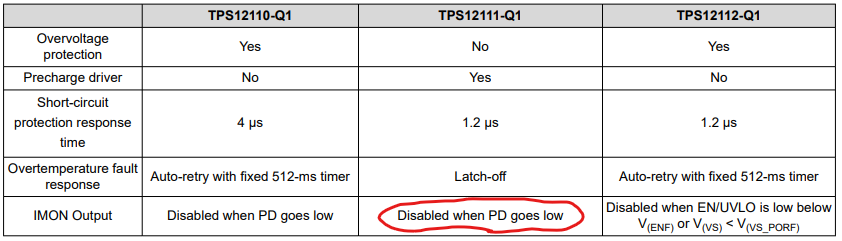

我们的客户正在考虑使用 TPS1211-Q1。

然后、我们要确保该器件的行为。

在正常操作中、它们将施加高信号(大约 3.3V) 从 MCU 到导通 FET 的 EN/UVLO 引脚上。

TPS1211-Q1 检测到故障后、MCU 会检测到该故障事件并将 EN/UVLO 驱动至低电平。

但是、它们的 MCU 低电平约为 0.4V、高于 VENF (0.3V)、因此我想确保以防万一。

在这种情况下、MCU 的低电平信号仍低于 VUVLF (1.1V)、因此 TPS1211-Q1 关断 FET。

不过、低电平信号高于 VENF、因此我们无法保证该器件进入低 IQ 模式。

这种理解是否正确?

此致、

Kazuki Kuramochi