工具/软件:

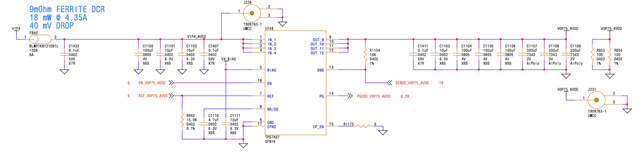

您好 — 使用下面的原理图,我们为 IC 提供 0.75V 的内核电压。 进一步位于 IC 的下游、封装上会有一个额外的 290uF 电容、而封装上会有 100uF 的电容(并联配置中的馈通电容)。 这样、我们始终看到电源上出现 25kHz 噪声、该噪声大约为 5mVpp — 随着电流的增加,峰峰值电压会增加(当消耗大约 1A 时、该噪声为 40mV)。

LDO 中是否有任何因素可以帮助解释这种现象? 谢谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好 — 使用下面的原理图,我们为 IC 提供 0.75V 的内核电压。 进一步位于 IC 的下游、封装上会有一个额外的 290uF 电容、而封装上会有 100uF 的电容(并联配置中的馈通电容)。 这样、我们始终看到电源上出现 25kHz 噪声、该噪声大约为 5mVpp — 随着电流的增加,峰峰值电压会增加(当消耗大约 1A 时、该噪声为 40mV)。

LDO 中是否有任何因素可以帮助解释这种现象? 谢谢!

尊敬的 Harrison:

感谢您与我们联系!

这听起来像是一个稳定性问题。 如果器件没有正相位裕度、它们将会振荡。

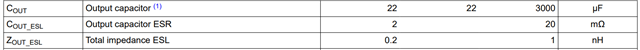

对于如此多的输出电容器、稳定性问题通常是因为电容过大或 ESR 降至最低要求以下。 鉴于我只在一个器件上添加了最多 1680uF 的电容、该电容应该能够占用 3000uF 的电容、ESR 可能是关键因素、具体取决于您使用的电容器。 该器件还具有 有助于实现稳定性的总阻抗 ESL 要求。

此致、

Gregory Thompson