工具/软件:

尊敬的团队:

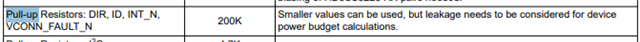

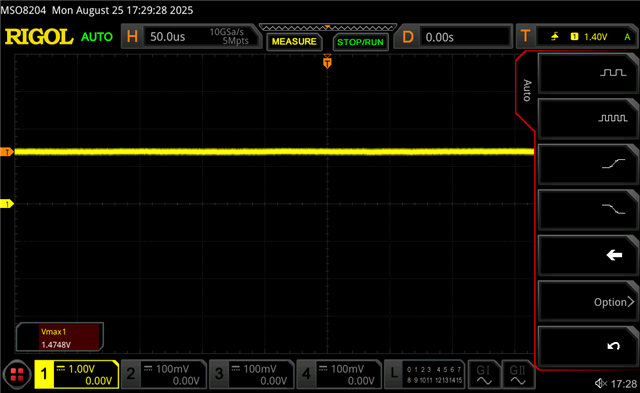

在中 HD3SS3220IRNHT 、我们连接了 ID 引脚 最终目的 1.8V 使用 200kΩ 上拉电阻器 。 但是、当 USB 端口设置为时 UFP(上行端口)模式 、ID 引脚电压下降到大约 295mV 而不是保持在 1.8V 左右。 实际上会得到同样的结果 100kΩ 、电压增加到大约 400mV 但仍然比预期的要低得多。 这是预期行为。 我们正在监控 ID 引脚以检测器件连接、由于电压电平较低、因此它可能会被错误地解释为器件连接。 对于 1.8V 电源、建议的上拉电阻值是否合适?

此致、

Sneha