工具/软件:

您好、

我将使用 BQ76972 实现 4S 智能电池设计、STM32H7 主机 MCU 通过配置为 400kHz 快速模式的 I2C 总线与电池监控器通信。 在分析 总线流量时、我观察到了一些特殊的 I2C 通信功能、并想向您寻求有关预计会出现哪些特性的指导。 最后、我希望验证我的硬件设计。 关于后者的几点说明:

-主机 MCU I2C 外设被配置为 400kHz 主模式,时钟延展被启用

- 主机 MCU 通过一对 LTC4331 差分扩展器与电池监控器通信,总线跨越多个 PCB。 值得注意的是、本地和远程 LTC4331 扩展器上的链路速率均配置为 500kHz。 请参阅下面显示的总线:

[MCU]<-I2C 400k、2K2 上拉电阻->[本地 LTC431]<双绞线差分对->[远程 LTC431] <-I2C 400k、2K7 上拉电阻-> [BQ76972 ]

下面附加的所有振荡镜/逻辑分析仪捕获结果都是在中的段上进行的 大胆。

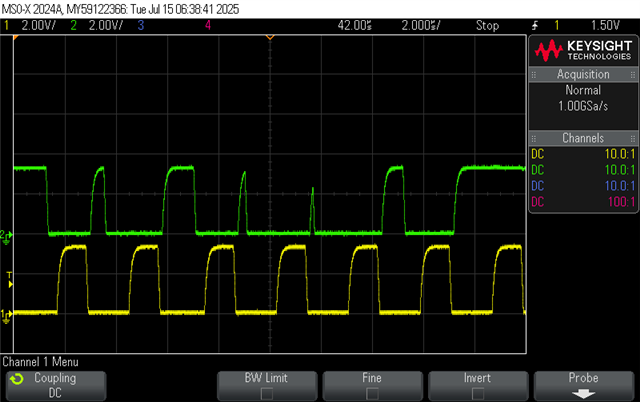

(1) SDA 干扰

虽然通信似乎正常工作、但我的示波器/逻辑分析仪 在 SDA 线路上显示了异常的“干扰“。 这些干扰是 SCL 时钟脉冲之间发生的非常短的脉冲、特别是当 SCL 线为低电平时。 在 SCL 的上升沿期间、SDA 信号似乎保持稳定、并且当 SCL 为高电平时、这些干扰似乎不会发生。

问题:是否预期出现故障且无害?

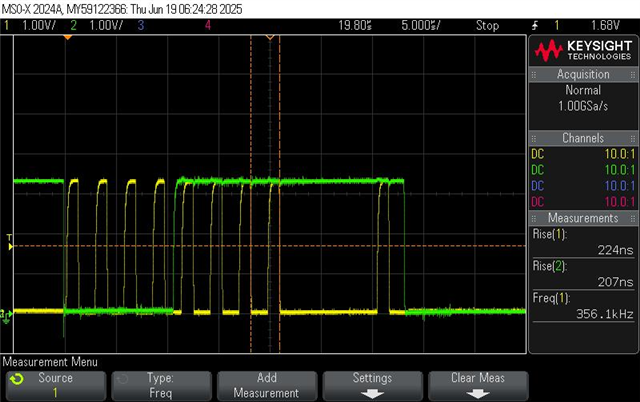

(2) 低于预期的时钟频率

我一直测量到 SCL 频率为~355kHz、低于预期的 400kHz。 数据表未明确指定预期的频率容差。 如上所述、差分 I2C 链路配置为 500kHz、而主机 MCU 配置为 400kHz、这表明它们不是瓶颈。

问题: 当器件配置为 400kHz I2C 快速模式时、预计实际的 BQ76972 SCL 频率是 355kHz 吗? 如果不是、 您是否怀疑较低的频率 是由主机/DIFF I2C 链路引起的?

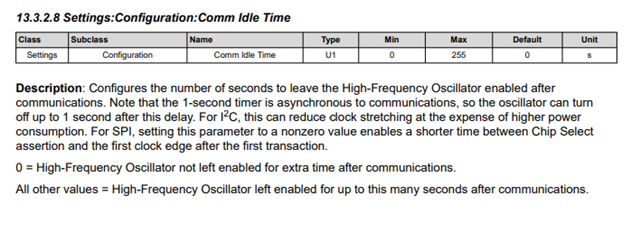

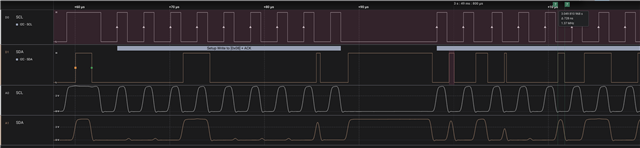

(3) 时钟延展过度

我观察到、在 400kHz 的频率下通过 I2C 与 BQ76972 通信时、时钟拉伸明显、这 极大地 影响了我的总线吞吐量。 如附加的逻辑分析仪捕获结果所示、器件会在字节之间将 SCL 线保持为低电平、持续的周期通常长于发送整个字节所需的时间、实际上是传输时间的两倍。

问题: 这种 激进的时钟延展是否被视为 BQ76972 的正常工作行为、或者它是否表明我的设置存在问题?

提前感谢您的时间和支持。

此致、

瓦西里