工具/软件:

大家好:

我是这个论坛的新成员,所以请原谅我,如果格式和写作没有遵循所有的规则。

我正在使用 ESP32 (MCU)、通过 I2C 读取和写入 BQ76952。

我将 BQ76952 配置为在 DFETOFF 引脚为低电平时触发预放电 (PDSG)。

然后、如果 LD 引脚和 PACK 引脚之间的电压差低于阈值(最大值)、则 DSG FET(放电 FET IO43)处于活动状态。

我的配置:

BQ76952 电源:

- BAT_PIN (IO47) 上为 12V

- 35V VC16 (IO48)

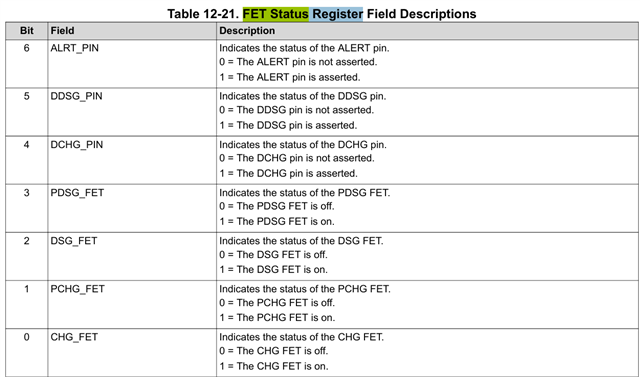

根据我读取的 FET 状态寄存器 (0x7F)、这种情况似乎有效:

-阶段 1:当 DFETOFF 为高电平时、FET 状态寄存器返回 97 (DEC)。

测量 CHG FET:23V(活动)

测量 DSG FET:0V(未激活)

测量 PCHG FET:28V

测量 PDSG:1.3V

-阶段 2:FET 状态寄存器在 DEFETOFFLOW(请求预放电)时返回 73 (DEC)。

CHG FET 测量:23V

DSG FET 测量:0V

PCHG FET 测量:28V

PDSG 测量:1.3V

-第 3 阶段:当 LD_PIN 达到 PACK_PIN 的值时、FET 状态寄存器返回 69 (DEC)。

CHG FET 测量:23V(活动)

DSG FET 测量:23V(活动)

PCHG FET 测量:28V

PDSG 测量:1.3V

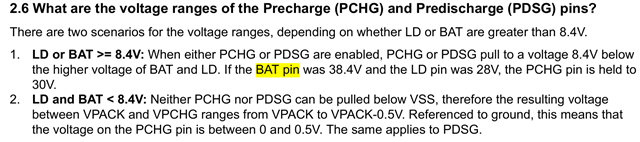

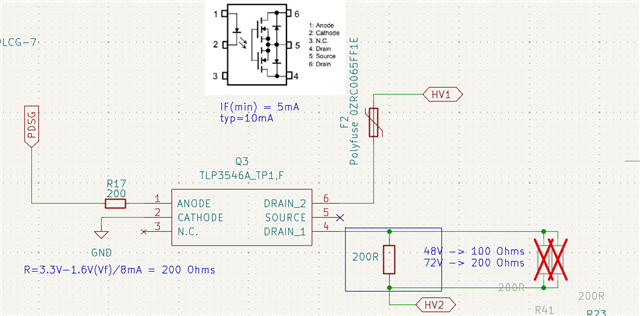

我使用 PDSG 引脚控制光耦合器以启用预充电。 当 PDSG 引脚处于活动状态时、我需要引脚上具有 3、3V 的电压。

我的问题如下:

-应该工作的 PDSG 引脚像 PCHG 引脚? 因此、输出处于 1.3V 正常吗?

-是否可以配置 PDSG 输出电压?

请参阅下面的 FET 状态寄存器: