主题中讨论的其他器件:TPS65987

工具/软件:

尊敬的 TI 团队:

我们有 TUSB1046A + TPS65987 原理图、

请您帮助查看我们的原理图吗? 此示意图与 Intel Twin Lake-N 或 Intel Panther Lake-H 平台搭配使用

我可以通过 私人消息发送原理图文件。

谢谢

Henry

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

尊敬的 TI 团队:

我们有 TUSB1046A + TPS65987 原理图、

请您帮助查看我们的原理图吗? 此示意图与 Intel Twin Lake-N 或 Intel Panther Lake-H 平台搭配使用

我可以通过 私人消息发送原理图文件。

谢谢

Henry

您好 Henry:

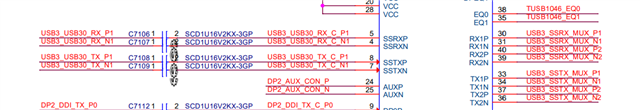

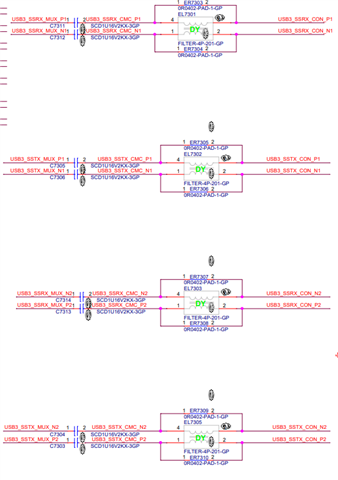

对于交流电容、 TX1/2 P/N、SSRX 和 SSTX 通道上只应有 100nF 电容。 RX1/2 P/N 不需要电容器、应移除这些电容器。

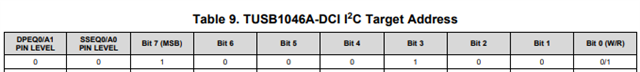

用于 3.3 I2C 的 I2C_EN 上拉。 看起来 I2C 会相应地被拉高。

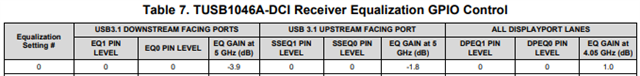

启动时、对于 EQ、所有 EQ 引脚都被下拉、默认电平为 0。 这些电平可通过 I2C 进行调整:

否则、我没有任何其他注释。

谢谢、

Ryan

您好 Henry:

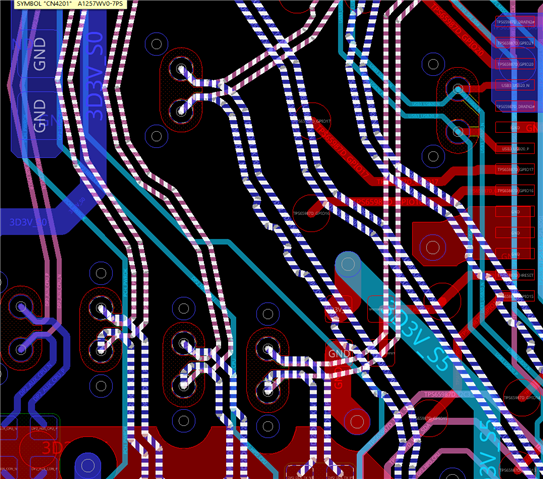

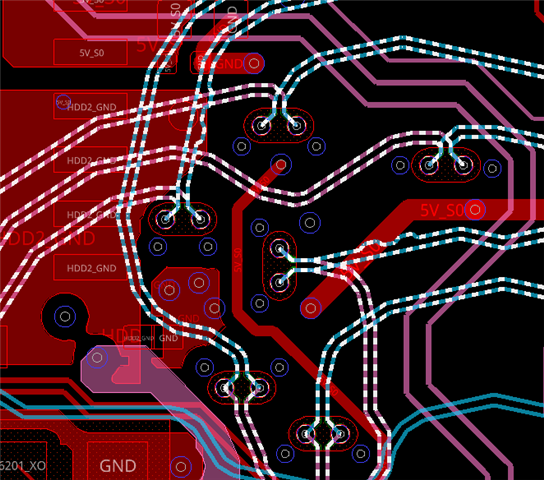

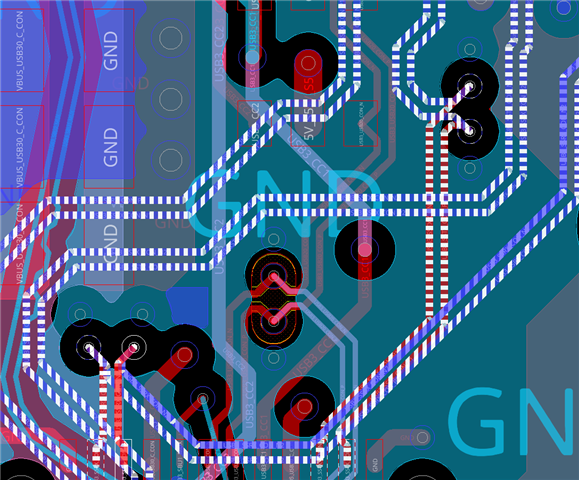

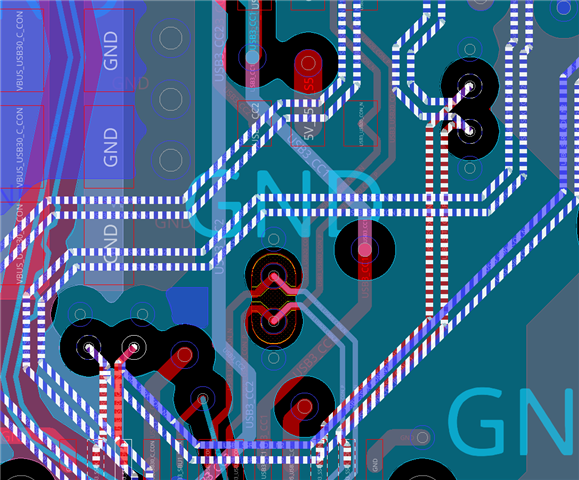

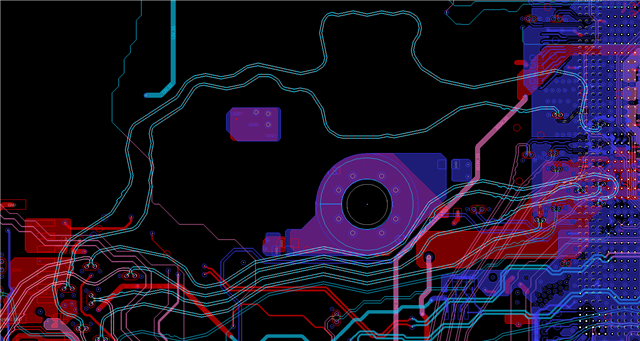

看起来多个信号在过孔处转动 180 度。 我们强烈建议不要这样做、因为这会导致信号中发生反射。 如果可能、我们建议在过孔处将这些信号校正、以避免这些反射并提高信号质量。

请确保差分对内延迟差也尽可能低。

然后、总体而言、对于 SOC 和转接驱动器之间的信号路径、信号路径中似乎有很多曲线和较大的绕组。 如果可能、我们建议对于布局设计、信号保持尽可能直、仅在需要时进行弯曲。 客户有这么多曲线的原因吗?

谢谢、

Ryan