工具/软件:

我们看到 组件主体上有各种各样的芯片输出(SMT 后处理)、如果存在可接受性要求、我们希望了解。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

我们看到 组件主体上有各种各样的芯片输出(SMT 后处理)、如果存在可接受性要求、我们希望了解。

您好 Bryan、

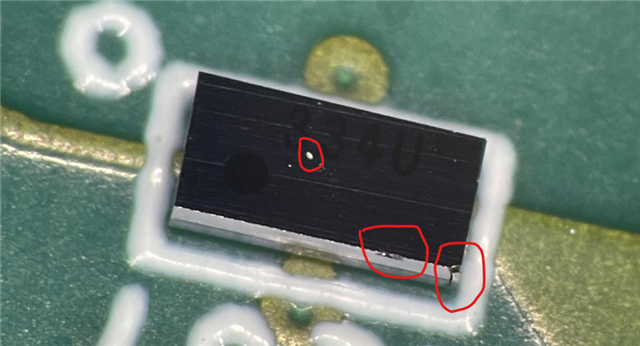

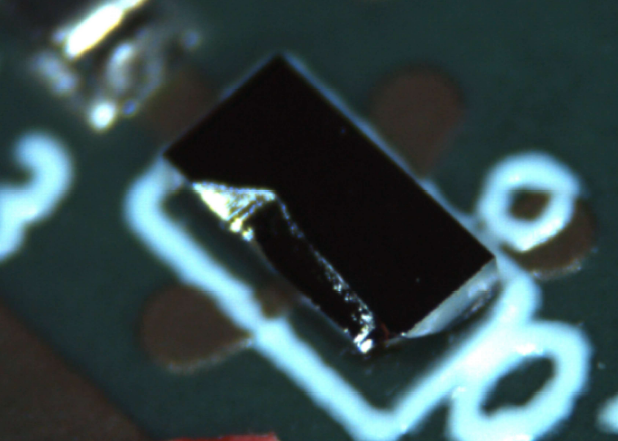

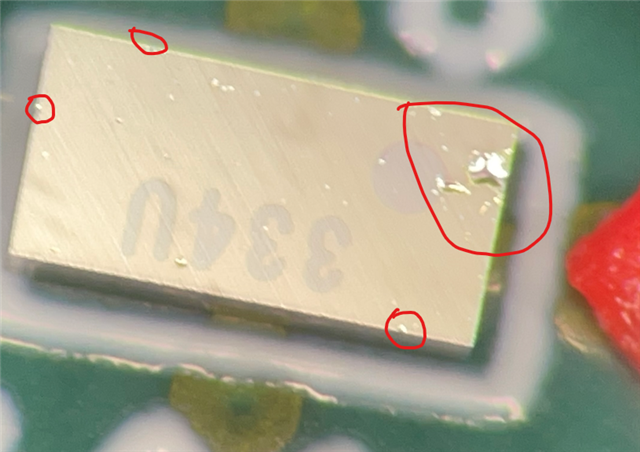

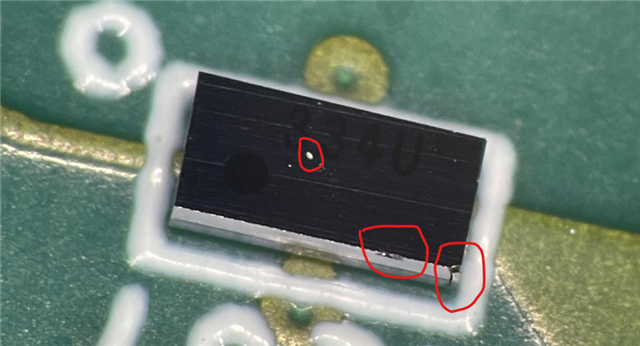

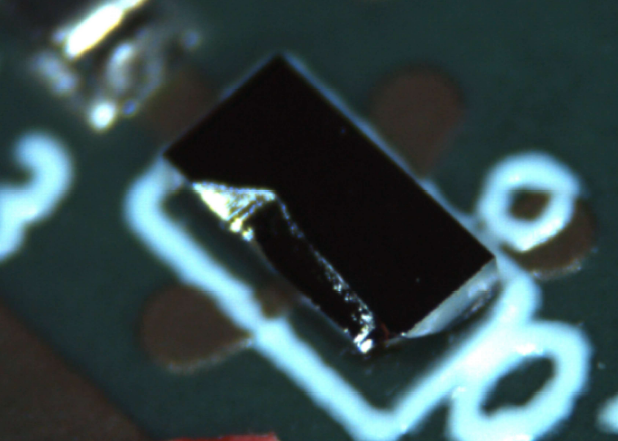

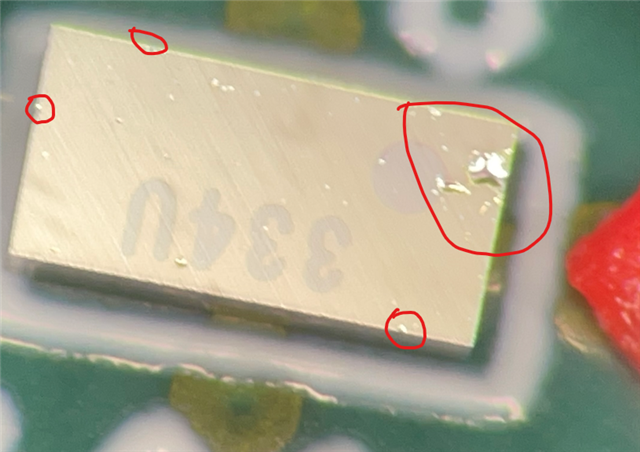

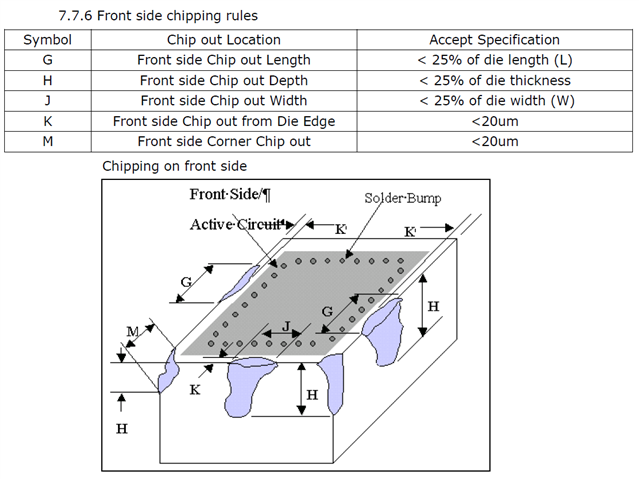

感谢您关注 TI FET。 背面(标识侧)排屑深度不应超过芯片厚度的 25%以及芯片长度或宽度的 50%。 下表和图中显示了前侧切屑规则。 前侧缺口的最大问题是芯片是否延伸到裸片的有效区域。 其中 2 张图片中显示的小缺口是可以接受的、并且在卷带包装之前将通过 TI 的光学检查。 第 3 张图片是不可接受的、也不会通过 TI 的光学检查。 我在下面提供了有关 TI 芯片级 FET 的一些有用链接。 它们本质上是具有可焊接焊盘或 BGA 互连的硅片。 在处理和组装到 PCB 上时需要小心。 如果您有任何问题、敬请告知。

FemtoFET SMT 指南: https://www.ti.com/lit/ug/slra003d/slra003d.pdf

解决芯片级功率 MOSFET 的组装问题: https://www.ti.com/lit/an/slvafh0/slvafh0.pdf

WCSP 处理指南: https://www.ti.com/lit/ml/sszqnf6/sszqnf6.pdf

WCSP/DSBGA 应用报告: https://www.ti.com/lit/an/snva009ai/snva009ai.pdf

此致、

约翰·华莱士

TI FET 应用