工具/软件:

大家好!

我对 PGOOD 上升时间有疑问。

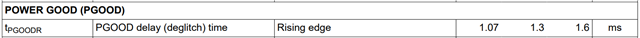

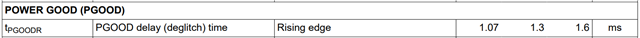

超过 PGTH 阈值 (~ 1.2V) 和 PGOOD 信号变为高电平有效之间的延迟时间是多少?

根据数据表规格、PGOOD 在 PGTH 达到 1.2V 后 1.3ms 变为高电平、但在实际测量中、PGOOD 在 20ms 后变为高电平。

为什么不是 1.3ms? 你知道的原因吗?

此致、

Ishiwata

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

大家好!

我对 PGOOD 上升时间有疑问。

超过 PGTH 阈值 (~ 1.2V) 和 PGOOD 信号变为高电平有效之间的延迟时间是多少?

根据数据表规格、PGOOD 在 PGTH 达到 1.2V 后 1.3ms 变为高电平、但在实际测量中、PGOOD 在 20ms 后变为高电平。

为什么不是 1.3ms? 你知道的原因吗?

此致、

Ishiwata

您好 Amrit、

我发送了一封关于以下内容的私人邮件、但尚未收到回复。

请回复。

当超过 PGTH 阈值(约 1.2V)时、数据表中 PGOOD 信号变为高电平所需的时间为 1.3ms、但当我实际测量它时、它会在 20ms 内变为高电平。

您说 PGOOD 有时可以像下面电路图中的电压跟随器那样延迟到 20ms?94、是否可以使用相同的电阻和电容值?

此致、

Ishiwata

您好 Shuji、

很抱歉耽误您的时间、感谢您的耐心等待。

要使 PGOOD 提供两个条件必须满足 VOUT 高于 PGTH 且栅极电压高于 PGTHVth VGS。

这可确保内部 FET 完全导通(饱和区域)、并且完整电流可以流过器件。

大于 VGH+VTH 值的栅极电压通过内部 VGS 信号实现。

采取这些措施是为了保护内部 FET SOA。

在本例中、VOUT 压摆率较高、并且 PGTH 设置为非常低的值。 因此、即使 VOUT 超过 PGTH 值、PGOOD 在超过 VGHI 后变为高电平。

因此、当 VOUT 完全设置时、您会看到 PGOOD 变为高电平。

谢谢

Amrit

尊敬的 Shuji:

1.3 MS tPGOODR 是 cdVdT 打开时的状态。 这意味着它具有更快的压摆率。

当您具有 cdVdT CAP 时、VOUT 将具有较慢的压摆率来控制浪涌。

当 PGOOD 同时满足 数据表中提到的 PGTH 和内部 FET 高电平 (VGHI) 时、PGOOD 将变为高电平。 这就是为什么您会在 VOUT 稳定后看到 PGOOD 出现的原因。 这是预期行为。

您是否使用 EVM 确认了相同的内容:即 PGOOD 在 1.3ms 后上升?

是、如 EC 表中所述、在 EVM 上确认 cdvdt 电容器断开且 COUT:1uF。

谢谢

Amrit